Description:

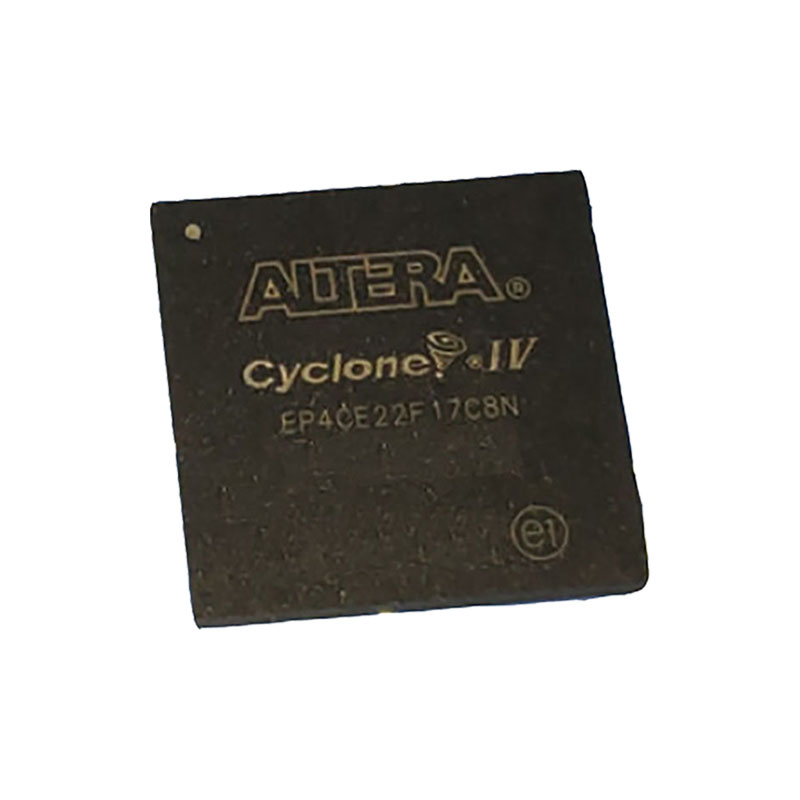

Product EP4CE22F17C8N belongs to Altera’s new Cyclone ® IV E FPGA device series. This series of products only requires two power sources, greatly simplifying the distribution network, reducing circuit board costs, minimizing circuit board space, and shortening design time. By utilizing integrated transceivers on chip architecture, motherboard design and integration can be simplified. In addition, the flexible transceiver clock architecture supports you to implement multiple protocols while fully utilizing all available transceiver resources.

The Cyclone IV E FPGA series is built on an optimized 60 nanometer low-power process, continuing the previous generation Cyclone ® The low-power leading advantage of III FPGA, while reducing the core voltage, has reduced the total power consumption by 25% compared to the previous generation product. Design implementation details can improve performance, reduce size, and lower power consumption. In the past, performance and size were automatically balanced within the register transfer level (RTL) through the layout and routing design process.

Applications:

Small applications:

Wireless field

Wired field

Broadcasting field

Industrial sector

Consumer and communication industries, etc

Cyclone IV Device Family Features

The cyclical redundancy check (CRC) error detection feature during user mode is supported in all Cyclone IV GX devices. For Cyclone IV E devices, this feature is only supported for the devices with the core voltage of 1.2 V.

■ Cyclone IV E—lowest power, high functionality with the lowest cost

■Cyclone IV E devices are offered in core voltage of 1.0 V and 1.2 V.

■Cyclone IV E devices are available in space-saving Enhanced Thin Quad Flat Pack (EQFP) and FineLine BGA (FBGA) packages with various I/O pin counts.

■ Low-cost, low-power FPGA fabric:

■ 6K to 150K logic elements

■ Up to 6.3 Mb of embedded memory

■ Up to 360 18 × 18 multipliers for DSP processing intensive applications

■ Protocol bridging applications for under 1.5 W total power

■ Up to 532 user I/Os

■ LVDS interfaces up to 840 Mbps transmitter (Tx), 875 Mbps Rx

■ Support for DDR2 SDRAM interfaces up to 200 MHz

■ Support for QDRII SRAM and DDR SDRAM up to 167 MHz

■ Up to eight phase-locked loops (PLLs) per device

■ Offered in commercial and industrial temperature grades

External Memory Specification for DDR2 SDRAM

In the Quartus II software version 10.0, the Cyclone IV E I8L speed grade supported full-rate DDR2 SDRAM with a maximum clock rate of up to 150 MHz on column and row I/Os. This maximum clock rate is a preliminary specification pending the finalization of the timing model.

In the Quartus II software version 10.0 SP1 and later, the Cyclone IV E I8L speed grade full-rate DDR2 SDRAM maximum clock rate specification on column and row I/Os has been revised due to the finalization of the timing model for the Cyclone IV E device family.

Device Family Variant and High-Speed Transceivers

The Cyclone IV device family contains two variants optimized to meet different application requirements. Cyclone IV GX devices contain up to eight full duplex high-speed transceivers that can operate independently at data rates up to 3.125 Gbps with physical coding sublayer (PCS) and physical media attachment (PMA) support, and a PCI Express hard IP block. Cyclone IV E devices are enhanced for lowest power, high functionality with the lowest cost. If your application requires high-speed transceivers up to 3.125 Gbps, choose a GX device variant. Otherwise, choose an E variant for high functionality with the lowest cost.

External Memory Interfaces

Cyclone IV devices support SDR, DDR, DDR2 SDRAM, and QDRII SRAM interfaces on the top,bottom, and right sides of the device. Cyclone IV E devices also support these interfaces on the left side of the device. Interfaces may span two or more sides of the device to allow more flexible board design. The Altera® DDR SDRAM memory interface solution consists of a PHY interface and a memory controller. Altera supplies the PHY IP and you can use it in conjunction with your own custom memory controller or an Altera-provided memory controller. Cyclone IV devices support the use of error correction coding (ECC) bits on DDR and DDR2 SDRAM interfaces.