Beschreibung:

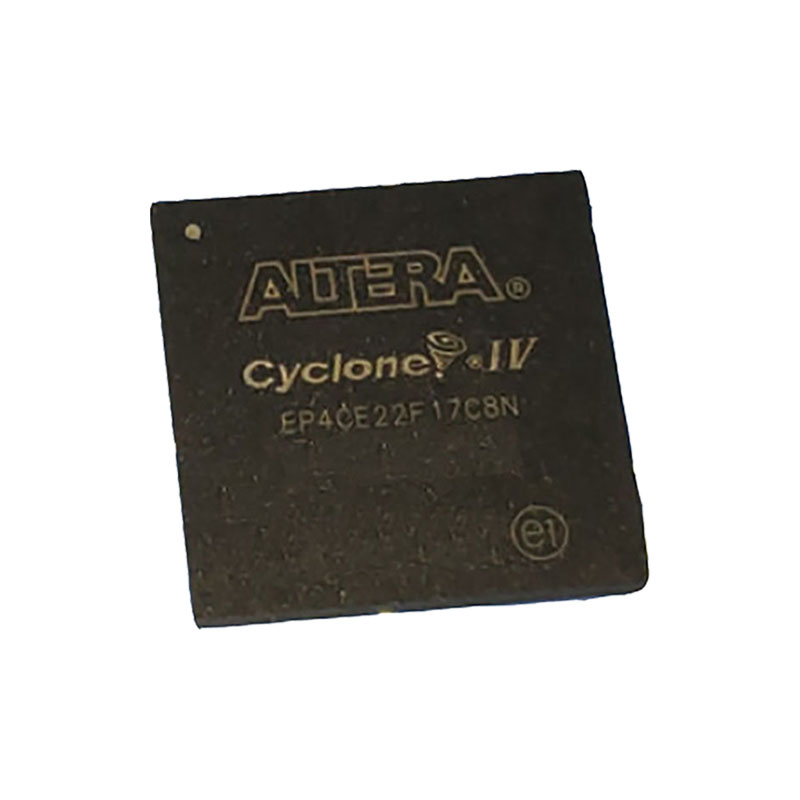

Das Produkt EP4CE22F17C8N gehört zur neuen Cyclone ® IV E FPGA-Bausteinserie von Altera. Diese Produktserie benötigt nur zwei Stromquellen, was das Verteilernetzwerk erheblich vereinfacht, die Kosten für die Leiterplatte senkt, den Platz auf der Leiterplatte minimiert und die Entwicklungszeit verkürzt. Durch die Verwendung von integrierten Transceivern in der Chip-Architektur können das Design und die Integration der Hauptplatine vereinfacht werden. Darüber hinaus können Sie dank der flexiblen Transceiver-Taktarchitektur mehrere Protokolle implementieren und dabei alle verfügbaren Transceiver-Ressourcen voll ausnutzen.

Die Cyclone IV E FPGA-Serie basiert auf einem optimierten 60-Nanometer-Low-Power-Prozess und setzt damit die vorherige Generation des Cyclone ® fort. Der führende Vorteil des Low-Power-III-FPGAs bei gleichzeitiger Reduzierung der Core-Spannung hat den Gesamtstromverbrauch um 25% im Vergleich zum Produkt der vorherigen Generation gesenkt. Details der Design-Implementierung können die Leistung verbessern, die Größe reduzieren und den Stromverbrauch senken. In der Vergangenheit wurden Leistung und Größe automatisch innerhalb der Registertransferebene (RTL) durch den Layout- und Routing-Designprozess ausgeglichen.

Anwendungen:

Kleine Anwendungen:

Drahtloses Feld

Verdrahtetes Feld

Bereich Broadcasting

Industrieller Sektor

Konsum- und Kommunikationsindustrie, etc.

Merkmale der Cyclone IV Gerätefamilie

Die Funktion der zyklischen Redundanzprüfung (CRC) zur Fehlererkennung im Benutzermodus wird von allen Cyclone IV GX-Geräten unterstützt. Bei Cyclone IV E-Geräten wird diese Funktion nur für Geräte mit einer Kernspannung von 1,2 V unterstützt.

■ Cyclone IV E - geringster Stromverbrauch, hohe Funktionalität bei niedrigsten Kosten

■Cyclone IV E Geräte werden mit einer Kernspannung von 1,0 V und 1,2 V angeboten.

■Cyclone IV E-Bausteine sind in platzsparenden Enhanced Thin Quad Flat Pack (EQFP)- und FineLine BGA (FBGA)-Gehäusen mit verschiedenen E/A-Pinzahlen erhältlich.

Kostengünstige, stromsparende FPGA-Fabric:

■ 6K bis 150K Logikelemente

■ Bis zu 6,3 Mb integrierter Speicher

■ Bis zu 360 18 × 18 Multiplikatoren für DSP-verarbeitungsintensive Anwendungen

■ Protokollüberbrückungsanwendungen für weniger als 1,5 W Gesamtleistung

■ Bis zu 532 Benutzer-E/As

■ LVDS-Schnittstellen mit bis zu 840 Mbps Sender (Tx), 875 Mbps Rx

■ Unterstützung für DDR2 SDRAM Schnittstellen bis zu 200 MHz

■ Unterstützung für QDRII SRAM und DDR SDRAM bis zu 167 MHz

■ Bis zu acht PLLs (Phase-Locked-Loops) pro Gerät

■ Erhältlich in kommerziellen und industriellen Temperaturklassen

Externer Speicher Spezifikation für DDR2 SDRAM

In der Quartus II Software Version 10.0 unterstützte der Cyclone IV E I8L Speed Grade DDR2 SDRAM mit einer maximalen Taktrate von bis zu 150 MHz an Spalten- und Zeilen-I/Os. Diese maximale Taktrate ist eine vorläufige Spezifikation, die bis zur Fertigstellung des Timing-Modells gilt.

In der Quartus II Software Version 10.0 SP1 und später wurde die Spezifikation für die maximale Taktrate von DDR2 SDRAM der Geschwindigkeitsklasse Cyclone IV E I8L auf Spalten- und Zeilen-I/Os aufgrund der Fertigstellung des Timing-Modells für die Cyclone IV E Bausteinfamilie überarbeitet.

Variante der Gerätefamilie und Hochgeschwindigkeits-Transceiver

Die Cyclone IV-Gerätefamilie enthält zwei Varianten, die für unterschiedliche Anwendungsanforderungen optimiert sind. Cyclone IV GX-Bausteine enthalten bis zu acht Vollduplex-Hochgeschwindigkeits-Transceiver, die unabhängig voneinander mit Datenraten von bis zu 3,125 Gbit/s arbeiten können und den Physical Coding Sublayer (PCS) und Physical Media Attachment (PMA) unterstützen, sowie einen PCI Express Hard IP-Block. Die Cyclone IV E-Bausteine sind optimiert für niedrigsten Stromverbrauch, hohe Funktionalität und niedrige Kosten. Wenn Ihre Anwendung Hochgeschwindigkeits-Transceiver mit bis zu 3,125 Gbps benötigt, wählen Sie eine GX-Bausteinvariante. Andernfalls wählen Sie eine E-Variante für hohe Funktionalität bei niedrigsten Kosten.

Externe Speicherschnittstellen

Cyclone IV-Geräte unterstützen SDR-, DDR-, DDR2 SDRAM- und QDRII SRAM-Schnittstellen an der oberen, unteren und rechten Seite des Geräts. Cyclone IV E-Geräte unterstützen diese Schnittstellen auch auf der linken Seite des Geräts. Die Schnittstellen können sich über zwei oder mehr Seiten des Bausteins erstrecken, um ein flexibleres Board-Design zu ermöglichen. Die Altera® DDR SDRAM Speicherschnittstellenlösung besteht aus einer PHY-Schnittstelle und einem Speichercontroller. Altera liefert die PHY-IP und Sie können sie in Verbindung mit Ihrem eigenen Speichercontroller oder einem von Altera bereitgestellten Speichercontroller verwenden. Cyclone IV Bausteine unterstützen die Verwendung von ECC-Bits (Error Correction Coding) auf DDR und DDR2 SDRAM Schnittstellen.