Beschreibung:

Der CY15B104Q ist ein nichtflüchtiger 4-Mbit-Speicher, der einen fortschrittlichen ferroelektrischen Prozess verwendet. Ein ferroelektrischer Direktzugriffsspeicher oder F-RAM ist nicht flüchtig und führt Lese- und Schreibvorgänge ähnlich wie ein RAM durch. Er bietet eine zuverlässige Datenspeicherung für 151 Jahre und eliminiert die Komplexität, den Overhead und die Zuverlässigkeitsprobleme auf Systemebene, die durch seriellen Flash, EEPROM und andere nichtflüchtige Speicher verursacht werden.

Im Gegensatz zu seriellem Flash und EEPROM führt der CY15B104Q Schreibvorgänge mit Busgeschwindigkeit aus. Es entstehen keine Schreibverzögerungen. Die Daten werden sofort in das Speicherarray geschrieben, nachdem jedes Byte erfolgreich an das Gerät übertragen wurde. Der nächste Buszyklus kann beginnen, ohne dass eine Datenabfrage erforderlich ist. Darüber hinaus bietet das Produkt im Vergleich zu anderen nichtflüchtigen Speichern eine beträchtliche Schreibausdauer. Der CY15B104Q ist in der Lage, 1014 Lese-/Schreibzyklen zu unterstützen, das sind 100 Millionen Mal mehr Schreibzyklen als EEPROM.

Diese Fähigkeiten machen den CY15B104Q ideal für nichtflüchtige Speicheranwendungen, die häufige oder schnelle Schreibvorgänge erfordern. Beispiele reichen von der Datenerfassung, bei der die Anzahl der Schreibzyklen entscheidend sein kann, bis hin zu anspruchsvollen industriellen Steuerungen, bei denen die lange Schreibzeit von seriellem Flash oder EEPROM zu Datenverlust führen kann.

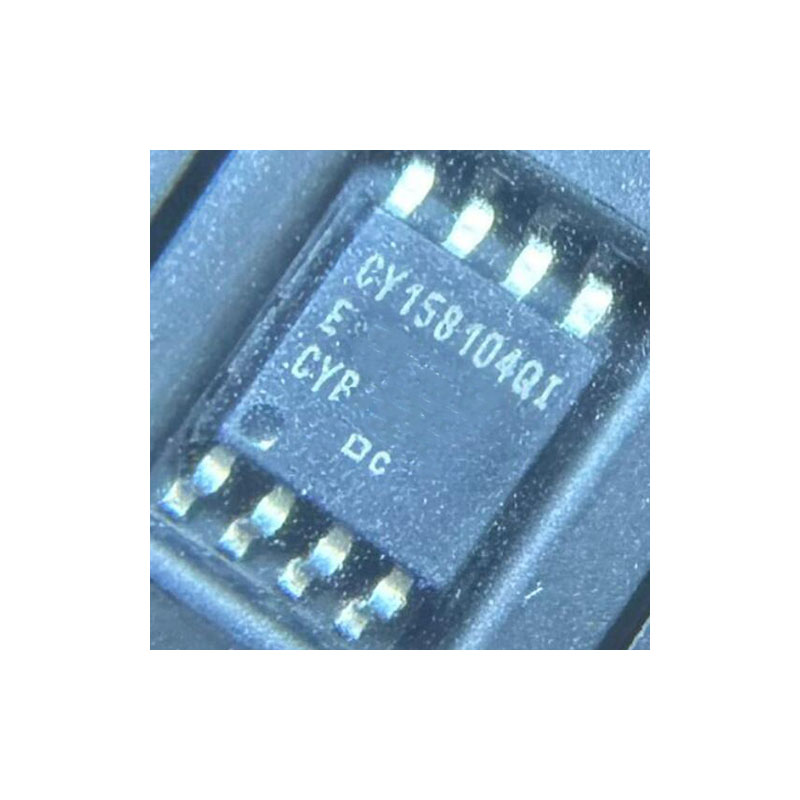

Der CY15B104Q bietet Anwendern von seriellem EEPROM oder Flash erhebliche Vorteile als Hardware-Ersatz. Der CY15B104Q verwendet den Hochgeschwindigkeits-SPI-Bus, der die Hochgeschwindigkeits-Schreibfähigkeit der F-RAM-Technologie verbessert. Das Gerät verfügt über eine schreibgeschützte Geräte-ID, die es dem Host ermöglicht, den Hersteller, die Produktdichte und die Produktrevision zu ermitteln. Die Spezifikationen des Bausteins sind über einen industriellen Temperaturbereich von -40 °C bis +85 °C.

Eigenschaften:

4-Mbit ferroelektrischer Direktzugriffsspeicher (F-RAM), logisch organisiert als 512 K × 8

Hohe Ausdauer 100 Billionen (1014) Lese-/Schreibvorgänge

151 Jahre Datenspeicherung

NoDelay™ schreibt

Fortschrittlicher, hochzuverlässiger ferroelektrischer Prozess

Sehr schnelle serielle Peripherieschnittstelle (SPI)

Bis zu 40-MHz-Frequenz

Direkter Hardware-Ersatz für seriellen Flash und EEPROM

Unterstützt SPI Modus 0 (0, 0) und Modus 3 (1, 1)

Hochentwickeltes Schreibschutzsystem

Hardware-Schutz über den Write Protect (WP) Pin

Softwareschutz mit der Anweisung Write Disable

Software-Blockierschutz für 1/4, 1/2 oder das gesamte Array

Hersteller-ID und Produkt-ID

Niedriger Stromverbrauch

300 mA Wirkstrom bei 1 MHz

100 mA (typ) Standby-Strom

3 mA (typ) Strom im Schlafmodus

Low-Voltage-Betrieb: VDD = 2,0 V bis 3,6 V

Industrielle Temperatur: -40 °C bis +85 °C

Konform mit der Richtlinie zur Beschränkung gefährlicher Stoffe (RoHS)

Anwendungen:

Ein völlig neuer Lebensstil und ein neues Gesundheitserlebnis für den vernetzten Bürger von heute

Unterhaltungselektronik

Weltraumanwendungen

Übersicht

Der CY15B104Q ist ein serieller F-RAM-Speicher. Das Speicherarray ist logisch als 524.288 × 8 Bit organisiert und wird über einen Industriestandard-SPI-Bus (Serial Peripheral Interface) angesprochen. Die Funktionsweise des F-RAM ist ähnlich wie bei seriellem Flash und seriellen EEPROMs. Der Hauptunterschied zwischen dem CY15B104Q und einem seriellen Flash oder EEPROM mit der gleichen Pinbelegung ist die überlegene Schreibleistung des F-RAM, die hohe Ausdauer und der geringe Stromverbrauch.

Speicherarchitektur

Beim Zugriff auf den CY15B104Q adressiert der Benutzer 512K Speicherplätze mit jeweils acht Datenbits. Diese acht Datenbits werden seriell hinein- oder herausgeschoben. Der Zugriff auf die Adressen erfolgt über das SPI-Protokoll, das eine Chipauswahl (um mehrere Geräte auf dem Bus zuzulassen), einen Opcode und eine Drei-Byte-Adresse enthält. Die oberen 5 Bits des Adressbereichs sind 'don't care'-Werte. Die vollständige Adresse von 19 Bits spezifiziert jedes Byte Adresse eindeutig. Die meisten Funktionen des CY15B104Q werden entweder über die SPI-Schnittstelle gesteuert oder von der integrierten Schaltung übernommen. Die Zugriffszeit für den Speicherbetrieb ist im Wesentlichen gleich Null, abgesehen von der Zeit, die für das serielle Protokoll benötigt wird. Das heißt, der Speicher wird mit der Geschwindigkeit des SPI-Busses gelesen oder geschrieben. Anders als bei einem seriellen Flash oder EEPROM ist es nicht notwendig, den Baustein auf eine Bereitschaftsbedingung hin abzufragen, da Schreibvorgänge mit Busgeschwindigkeit erfolgen. Bis eine neue Bustransaktion in das Gerät geschoben werden kann, ist ein Schreibvorgang abgeschlossen. Dies wird im Abschnitt über die Schnittstelle ausführlicher erklärt.