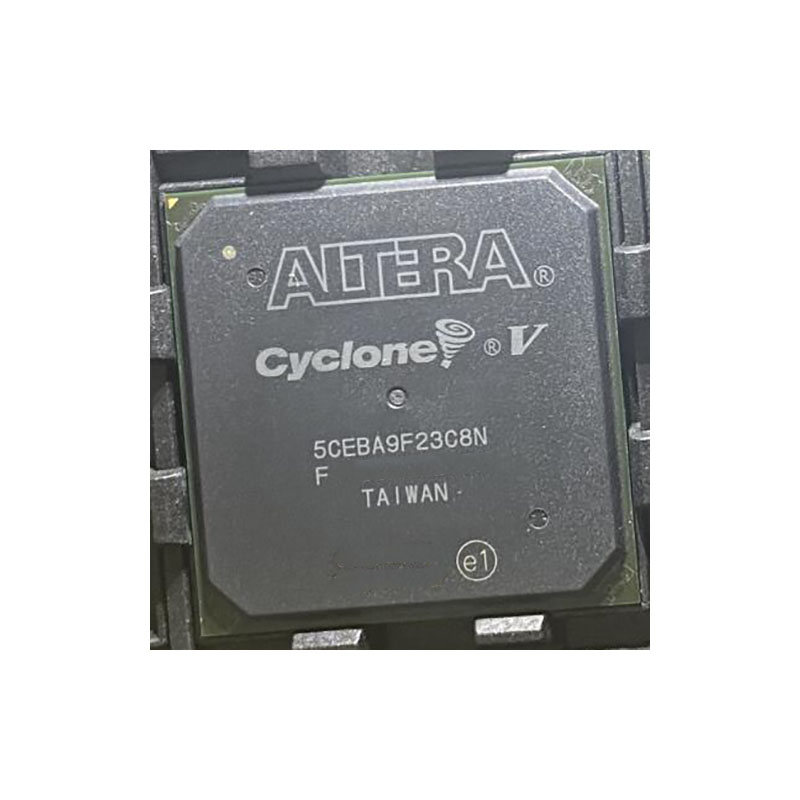

Beschreibung:

Die CycloneV Geräte sind so konzipiert, dass sie gleichzeitig den sinkenden Stromverbrauch, die Kosten und die Markteinführungszeit und die steigenden Bandbreitenanforderungen für hochvolumige und kostensensitive Anwendungen.

Cyclone V E sind für die niedrigsten Systemkosten und den geringsten Leistungsbedarf für ein breites Spektrum von allgemeinen Logik- und DSP-Anwendungen optimiert.

Die wichtigsten Vorteile der Cyclone® V Geräte

Geringerer Stromverbrauch

Basiert auf der 28 nm Low-Power (28LP) Prozesstechnologie von TSMC und enthält eine Fülle von Blöcken mit hartem geistigem Eigentum (IP). Bis zu 40% geringerer Stromverbrauch als bei der vorherigen Generation

Verbesserte Logikintegration und Differenzierungsmöglichkeiten

Adaptives Logikmodul mit 8 Eingängen (ALM)

Bis zu 13,59 Megabit (Mb) eingebetteter Speicher

Digitale Signalverarbeitungsblöcke (DSP) mit variabler Genauigkeit

Erhöhte Bandbreitenkapazität

- Gabits pro Sekunde (Gbps) und 144 Gbpstransceiver

- Festspeicher-Controller

Festes Prozessorsystem (HPS) mit integriertem Arm* Kortex* -A9 MPCore* Prozessor

Enge Integration eines Dual-Core Arm* Cortex* -A9 MPCore* Prozessors, harter IP und eines FPGA in einem einzigen Cyclone® V System-on-a-Chip (SoC)

Unterstützt eine Spitzenbandbreite von über 128 Gbps mit integrierter Datenkohärenz zwischen dem Prozessor und der FPGA-Fabric

Geringste Systemkosten

Benötigt nur zwei Kernspannungen für den Betrieb

Erhältlich in preiswerter Drahtbondverpackung

Enthält innovative Funktionen wie Konfiguration über Protokoll (CvP) und teilweise Rekonfiguration

Eigenschaften

Technologie

- Die 28-nm-Low-Power (28LP)-Prozesstechnologie von TSMC

- 1,1 V Kernspannung

Verpackung

- Wirebond-Pakete mit niedrigem Halogengehalt

- Mehrere Gerätedichten mit kompatiblen Gehäusegrundrissen für eine nahtlose Migration zwischen verschiedenen Gerätedichten

- RoHS-konforme und verbleite(1)Optionen

Leistungsstarke FPGA-Fabric Verbesserter ALM mit 8 Eingängen und vier Registern

Interne Speicherblöcke

- M10K-10-Kilobit (Kb) Speicherblöcke mit weichem Fehlerkorrekturcode (ECC)

- Memory Logic Array Block (MLAB)-640-Bit verteilter LUTRAM, bei dem Sie bis zu 25% der ALMs als MLAB-Speicher verwenden können

Eingebettete Hard-IP-Blöcke

DSP mit variabler Genauigkeit

- Native Unterstützung für bis zu drei Präzisionsstufen der Signalverarbeitung (drei 9 x 9, zwei 18 x 18 oder ein 27 x 27 Multiplikator) im selben DSP-Block mit variabler Genauigkeit

- 64-Bit-Akkumulator und Kaskade

- Eingebetteter interner Koeffizientenspeicher

- Preadder/Subtraktor für mehr Effizienz

Speicher-Controller DDR3, DDR2 und LPDDR2 mit 16 und 32 Bit ECC-Unterstützung

Eingebetteter Transceiver I/O PCI Express* (PCIe*) Gen2 und Gen1 (x1, x2 oder x4) hard IP mit Multifunktionsunterstützung, Endpunkt und Root Port

Uhrennetzwerke

- Globales Taktnetzwerk mit bis zu 550 MHz

- Globale, Quadranten- und periphere Taktnetzwerke

- Nicht genutzte Taktnetzwerke können abgeschaltet werden, um den dynamischen Stromverbrauch zu reduzieren.

Phasenverriegelungsschleifen (PLLs)

- Präzise Taktsynthese, Kompensation der Taktverzögerung und Zero Delay Buffering (ZDB)

- Ganzzahliger Modus und gebrochener Modus

FPGA Mehrzweck-E/As (GPIOs)

- 875 Megabit pro Sekunde (Mbps) LVDS-Empfänger und 840 Mbps LVDS-Sender

- 400 MHz/800 Mbps externe Speicherschnittstelle

- On-Chip-Terminierung (OCT)

- 3,3 V Unterstützung mit bis zu 16 mA Ansteuerungsstärke

Serielle Hochgeschwindigkeitsschnittstelle mit geringem Stromverbrauch

- 614 Mbps bis 6,144 Gbps integrierte Transceiver-Geschwindigkeit

- Vorverzerrung beim Senden und Entzerrung beim Empfänger

- Dynamische teilweise Rekonfiguration einzelner Kanäle

HPS (nur Cyclone V SE, SX und ST Geräte)

- Ein- oder Zwei-Kern Arm Cortex-A9 MPCore Prozessor - bis zu 925 MHz maximale Frequenz mit Unterstützung für symmetrisches und asymmetrisches Multiprocessing

- Schnittstellenperipherie - 10/100/1000 Ethernet Media Access Control (EMAC), USB 2.0 On-The-GO (OTG) Controller, Quad Serial Peripheral Interface (QSPI) Flash Controller, NAND Flash Controller, Secure Digital/MultiMediaCard (SD/MMC) Controller, UART, Controller Area Network (CAN), Serial Peripheral Interface (SPI), I2C Interface und bis zu 85 HPS GPIO

Schnittstellen

- Systemperipherie - Allzweck-Timer, Watchdog-Timer, DMA-Controller (Direct Memory Access), FPGA-Konfigurationsmanager sowie Takt- und Reset-Manager

- On-Chip-RAM und Boot-ROM

- HPS-FPGA-Brücken - umfassen die FPGA-zu-HPS-, HPS-zu-FPGA- und Lightweight-HPS-zu-FPGA-Brücken, die es der FPGA-Fabric ermöglichen, Transaktionen an Slaves im HPS auszugeben und umgekehrt

- FPGA-zu-HPS-SDRAM-Controller-Subsystem - stellt eine konfigurierbare Schnittstelle zum Multiport Front End (MPFE) des HPS-SDRAM-Controllers bereit

- Arm CoreSight™ JTAG-Debug-Zugangsport, Trace-Port und On-Chip-Trace-Speicher

Konfiguration

- Manipulationsschutz - Umfassender Designschutz zum Schutz Ihrer wertvollen IP-Investitionen

- Verbesserte Sicherheitsmerkmale des erweiterten Verschlüsselungsstandards (AES)

- CvP

- Dynamische Rekonfiguration des FPGAs

- Aktive serielle (AS) x1 und x4, passive serielle (PS), JTAG und schnelle passive parallele (FPP) x8 und x16 Konfigurationsoptionen

- Internes Schrubben

- Teilweise Rekonfiguration

Anwendungen:

Der mit integrierten Transceivern und Hard Memory Controllern ausgestattete Cyclone® V Geräte eignen sich für Anwendungen in der Industrie, im drahtlosen und drahtgebundenen Bereich, im Militär und in der Automobilindustrie.