DESCRIPCIÓN GENERAL

El HMC641ALP4E es un conmutador de propósito general, no reflectante, unipolar, de cuatro tiros (SP4T) fabricado mediante un proceso de arseniuro de galio (GaAs). Este conmutador ofrece alto aislamiento, baja pérdida de inserción y terminación en chip de los puertos aislados.

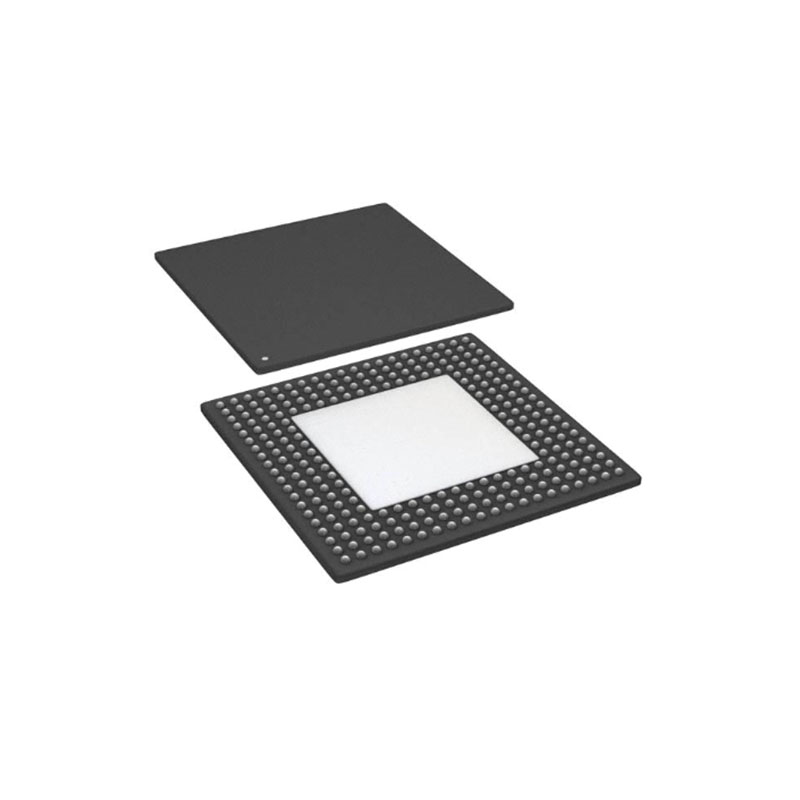

El HMC641ALP4E incluye un decodificador binario de 2 a 4 líneas en el chip que proporciona control lógico a partir de dos líneas lógicas de entrada. El HMC641ALP4E se presenta en un encapsulado LFCSP de 24 terminales de 4 mm × 4 mm y funciona entre 0,1 GHz y 20 GHz.

CARACTERÍSTICAS

Gama de frecuencias de banda ancha: 0,1 GHz a 20 GHz

Diseño no reflectante de 50 Ω

Baja pérdida de inserción: 3,0 dB a 20 GHz

Alto aislamiento: 40 dB a 20 GHz

Alta linealidad de entrada de 250 MHz a 20 GHz

P1dB: 24 dBm típico

IP3: 41 dBm típico

Alta potencia

26,5 dBm por trayecto

23 dBm trayecto terminado

Decodificador integrado de 2 a 4 líneas

Encapsulado LFCSP de 24 terminales, 4 mm × 4 mm

Clasificación ESD: 250 V (Clase 1A)

APLICACIONES

Instrumentos de prueba

Radios de microondas y terminales de muy pequeña apertura (VSAT)

Radios militares, radares y contramedidas electrónicas (ECM)

Sistemas de telecomunicaciones de banda ancha

TEORÍA DE FUNCIONAMIENTO

El HMC641ALP4E requiere una tensión de alimentación negativa en la patilla VSS y dos entradas de control lógico en las patillas CTRLA y CTRLB para controlar el estado de las rutas de RF.

Dependiendo del nivel lógico aplicado a la patilla CTRLA y a la patilla CTRLB, una ruta de RF está en estado de pérdida de inserción mientras que las otras tres rutas están en estado de aislamiento (ver Tabla 4). La ruta de pérdida de inserción conduce la señal de RF entre la patilla de lanzamiento de RF y la patilla común de RF, mientras que las rutas de aislamiento proporcionan una alta pérdida entre las patillas de lanzamiento de RF terminadas en resistencias internas de 50 Ω y la ruta de pérdida de inserción.

La secuencia ideal de encendido es la siguiente:

- Puesta a tierra hasta el fondo del troquel.

- Enciende el VSS.

3.Encienda las entradas de control digital. El orden relativo de las entradas de control lógico no es importante. Sin embargo, alimentar las entradas de control digital antes que la alimentación VSS puede provocar una polarización directa y dañar las estructuras internas de protección ESD.

4.Aplique una señal de entrada RF. El diseño es bidireccional; la señal de entrada de RF puede aplicarse a la patilla RFC mientras que las patillas de lanzamiento de RF son las salidas, o la señal de entrada de RF puede aplicarse a las patillas de lanzamiento de RF mientras que la patilla RFC es la salida. Todos los pines RF están acoplados a 0 V, y no se requiere bloqueo de CC en los pines RF cuando el potencial de la línea RF es igual a 0 V.

La secuencia de apagado es inversa a la de encendido.

secuencia.

INFORMACIÓN SOBRE LA SOLICITUD

TRIBUNAL DE EVALUACIÓN

La EV1HMC641ALP4 es una placa de evaluación de 4 capas. Cada capa de cobre es de 0,5 oz (0,7 mil) y están separadas por materiales dieléctricos. La figura 14 muestra el apilamiento de esta placa de evaluación.

Todas las trazas de RF y CC se enrutan en la capa superior de cobre, mientras que las capas interior e inferior son planos conectados a tierra que proporcionan una tierra sólida para las líneas de transmisión de RF. El material dieléctrico superior es un Rogers RO4350 de 10 mil. Los materiales dieléctricos intermedio e inferior proporcionan resistencia mecánica. El grosor total de la placa es de aproximadamente 62 mil, lo que permite conectar los lanzadores subminiatura versión A (SMA) en los bordes de la placa.

Las líneas de transmisión de RF se diseñaron utilizando un modelo de guía de ondas coplanar (CPWG), con una anchura de traza de 16 mil y una distancia a tierra de 13 mil para una impedancia característica de 50 Ω. Para una puesta a tierra térmica y de RF óptima, disponga tantas vías pasantes chapadas como sea posible alrededor de las líneas de transmisión y debajo de la almohadilla expuesta del encapsulado.

La Figura 15 muestra la disposición de la placa de evaluación EV1HMC641ALP4 con la colocación de los componentes. El puerto de alimentación se conecta al punto de prueba VSS, J8, y las tensiones de control, CTRLA y CTRLB, se conectan a los puntos de prueba A y B, J6 y J7, y la referencia de tierra se conecta al punto de prueba GND, J9. En la traza de alimentación, VSS, utilice un condensador de bypass de 1000 pF para filtrar el ruido de alta frecuencia.

Los puertos de entrada y salida de RF (RFC, RF1, RF2, RF3 y RF4) están conectados a través de líneas de transmisión de 50 Ω a los lanzadores SMA, J1 a J5. Estos lanzadores SMA están soldados a la placa. Una línea de calibración pasante conecta los lanzadores despoblados J10 y J11; esta línea de transmisión estima la pérdida de la PCB sobre las condiciones ambientales que se están evaluando.