Descripción:

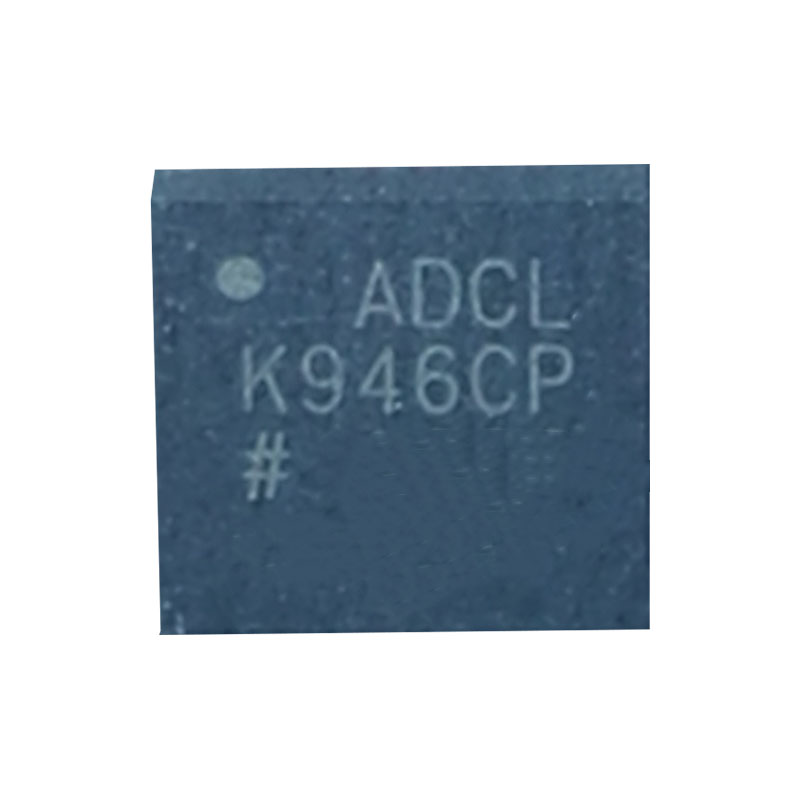

El ADCLK946BCPZ es un búfer de fanout de reloj ultrarrápido fabricado en el proceso bipolar de germanio de silicio (SiGe) XFCB3 patentado por Analog Devices, Inc. Este dispositivo está diseñado para aplicaciones de alta velocidad que requieren baja fluctuación.

El dispositivo tiene una entrada diferencial equipada con resistencias de terminación en chip de 100 Ω, diferenciales y con contacto central. La entrada acepta entradas LVPECL, CML, CMOS de 3,3 V acopladas en corriente continua (terminación simple) y CMOS de 1,8 V acopladas en corriente alterna, LVDS y LVPECL. Dispone de una clavija VREF para polarizar las entradas acopladas en alterna.

El ADCLK946BCPZ dispone de seis controladores de salida de lógica de emisor acoplado (ECL) de oscilación completa. Para el funcionamiento LVPECL (ECL positivo), polarice VCC a la alimentación positiva y VEE a tierra. Para el funcionamiento ECL, polarice VCC a tierra y VEE a la alimentación negativa.

Las etapas de salida ECL están diseñadas para conducir directamente 800 mV a cada lado en 50 Ω terminados a VCC - 2 V para un oscilación de salida diferencial total de 1,6 V.

Características:

Frecuencia de funcionamiento de 4,8 GHz

75 fs rms de fluctuación aleatoria de banda ancha

Terminaciones de entrada en chip

Alimentación de 3,3 V

Aplicaciones:

Sistemas de comunicación: como estaciones base inalámbricas, sistemas de comunicación por fibra óptica, comunicación por satélite, etc.

Convertidor de datos: fuente de reloj para convertidores de datos de alta velocidad como ADC, DAC, etc.

Generador de reloj: proporciona una señal de reloj muy estable para el sistema.

Instrumentación: Instrumentos como osciloscopios, generadores de señal, etc. que requieren fuentes de reloj de temporización de alta estabilidad.

DESCRIPCIÓN FUNCIONAL

ENTRADAS DE RELOJ

El ADCLK946 acepta una entrada de reloj diferencial y la distribuye a las seis salidas LVPECL.

La frecuencia máxima especificada es el punto en el que la oscilación de la tensión de salida es 50% de la oscilación LVPECL estándar.

El dispositivo tiene una entrada diferencial equipada con resistencias de terminación en chip de 100 Ω, diferenciales y con puntas centrales.

La entrada acepta LVPECL acoplado en CC, CML, CMOS de 3,3 V (un solo extremo) y CMOS acoplado en CA de 1,8 V, LVDS y LVPECL.

Dispone de una clavija VREF para la polarización de las entradas con acoplamiento acústico.

Mantenga la oscilación de tensión de entrada diferencial de aproximadamente 400 mV p-p a no más de 3,4 V p-p.Para varios esquemas de terminación de entrada de reloj.

El rendimiento del jitter de salida se degrada con una slew rate de entrada inferior a 1 V/ns.

El ADCLK946 está diseñado específicamente para minimizar el jitter aleatorio añadido en un amplio rango de slew rate de entrada.

Siempre que sea posible, sujete las señales de entrada excesivamente grandes con diodos Schottky rápidos, ya que los atenuadores reducen la velocidad de giro.

Los tramos de señal de entrada de más de unos pocos centímetros deben ser sobre dieléctricos de baja pérdida o cables con buenas características de alta frecuencia.

SALIDAS DE RELOJ

El rendimiento especificado requiere el uso de terminaciones de línea de transmisión adecuadas.

Las salidas LVPECL del ADCLK946 están diseñadas para conducir directamente 800 mV a un cable de 50 Ω o a líneas de transmisión microstrip/stripline terminadas con 50 Ω referenciadas a VCC - 2 V.

Las salidas están diseñadas para lograr la mejor adaptación de la línea de transmisión.

Si las señales de alta velocidad se deben encaminar más de un centímetro, se requiere la técnica de microstrip o la de stripline para garantizar tiempos de transición adecuados y evitar un anillamiento de salida excesivo y una dispersión de retardo de propagación dependiente del ancho de pulso.

La terminación equivalente a Venin utiliza una red de resistencias para proporcionar una terminación de 50 Ω a una tensión de CC que está por debajo de VOL del controlador LVPECL. En este caso, VS_DRV en el ADCLK946 debe ser igual a VCC del búfer receptor. Aunque la combinación de resistencias mostrada en la Figura 15 da como resultado un punto de polarización de c.c. de VS_DRV - 2 V, el voltaje de modo común real es VS_DRV - 1,3 V porque hay corriente adicional que fluye desde el controlador LVPECL.

ADCLK946 LVPECL a través de la resistencia pull-down. La terminación en Y de LVPECL es un esquema de terminación elegante que utiliza el menor número de componentes y ofrece adaptación de impedancia en modo par e impar. La adaptación de impedancia en modo par es una consideración importante para las líneas de transmisión estrechamente acopladas a altas frecuencias. Su principal inconveniente es que ofrece una flexibilidad limitada para variar la fuerza de accionamiento del driver LVPECL seguidor de emisor. Esto puede ser una consideración importante cuando la conducción largas longitudes de traza, pero por lo general no es un problema.