Descripción:

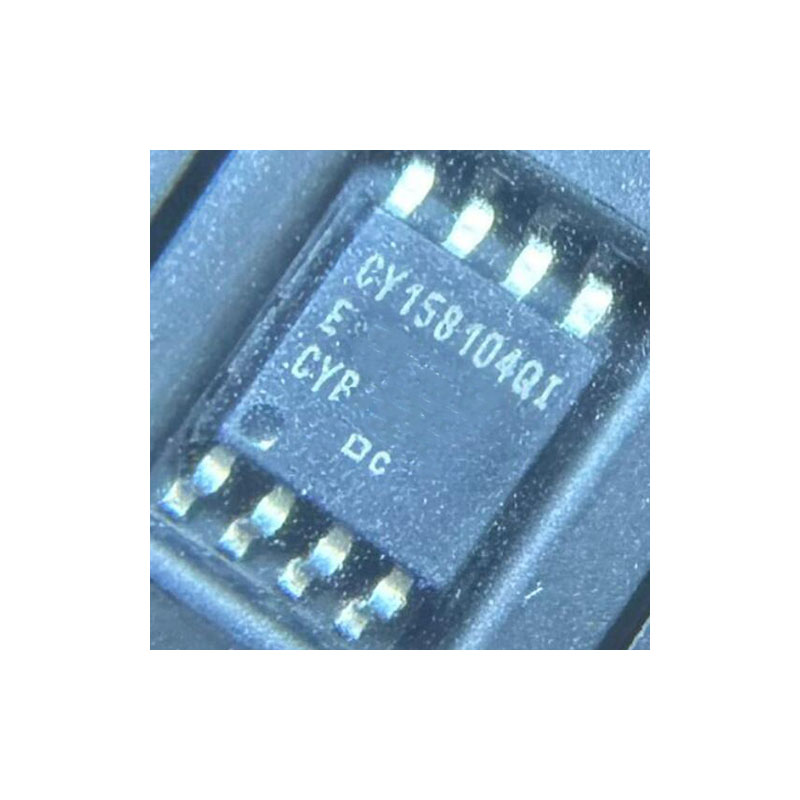

La CY15B104Q es una memoria no volátil de 4 Mbit que emplea un proceso ferroeléctrico avanzado. Una memoria ferroeléctrica de acceso aleatorio o F-RAM es no volátil y realiza lecturas y escrituras similares a una RAM. Proporciona una retención de datos fiable durante 151 años, al tiempo que elimina las complejidades, la sobrecarga y los problemas de fiabilidad a nivel de sistema causados por las memorias flash serie, EEPROM y otras memorias no volátiles.

A diferencia de la flash serie y la EEPROM, el CY15B104Q realiza operaciones de escritura a velocidad de bus. No se producen retardos de escritura. Los datos se escriben en la matriz de memoria inmediatamente después de que cada byte se transfiera con éxito al dispositivo. El siguiente ciclo de bus puede comenzar sin necesidad de sondeo de datos. Además, el producto ofrece una considerable resistencia a la escritura en comparación con otras memorias no volátiles. La CY15B104Q es capaz de soportar 1014 ciclos de lectura/escritura, o 100 millones de veces más ciclos de escritura que la EEPROM.

Estas capacidades hacen que el CY15B104Q sea ideal para aplicaciones de memoria no volátil que requieren escrituras frecuentes o rápidas. Los ejemplos van desde la recopilación de datos, donde el número de ciclos de escritura puede ser crítico, hasta los exigentes controles industriales donde el largo tiempo de escritura de la flash serie o la EEPROM puede provocar la pérdida de datos.

El CY15B104Q proporciona ventajas sustanciales a los usuarios de EEPROM serie o flash como sustituto de hardware. El CY15B104Q utiliza el bus SPI de alta velocidad, que mejora la capacidad de escritura a alta velocidad de la tecnología F-RAM. El dispositivo incorpora un ID de dispositivo de sólo lectura que permite al host determinar el fabricante, la densidad del producto y la revisión del producto. Las especificaciones del dispositivo están garantizadas en un rango de temperatura industrial de -40 °C a +85 °C.

Características:

Memoria ferroeléctrica de acceso aleatorio (F-RAM) de 4 Mbit organizada lógicamente como 512 K × 8

Alta resistencia 100 billones (1014) de lecturas/escrituras

151 años de conservación de datos

NoDelay™ escribe

Proceso ferroeléctrico avanzado de alta fiabilidad

Interfaz periférica serie (SPI) muy rápida

Frecuencia de hasta 40 MHz

Sustitución directa por hardware de flash serie y EEPROM

Admite los modos SPI 0 (0, 0) y 3 (1, 1)

Sofisticado esquema de protección contra escritura

Protección por hardware mediante la patilla de protección contra escritura (WP)

Protección por software mediante la instrucción Write Disable

Protección por bloque de software para 1/4, 1/2 o toda la matriz

ID de fabricante e ID de producto

Bajo consumo de energía

300 mA corriente activa a 1 MHz

100 mA (típica) corriente de espera

3 mA (típica) Corriente en modo de espera

Funcionamiento a bajo voltaje: VDD = 2,0 V a 3,6 V

Temperatura industrial: -40 °C a +85 °C

Cumple la restricción de sustancias peligrosas (RoHS)

Aplicaciones:

Un nuevo estilo de vida y una nueva experiencia de salud para el ciudadano conectado de hoy.

Electrónica de consumo

Aplicaciones espaciales

Visión general

La CY15B104Q es una memoria F-RAM serie. La matriz de memoria está organizada lógicamente como 524.288 × 8 bits y se accede a ella utilizando un bus de interfaz periférica serie (SPI) estándar de la industria. El funcionamiento de la F-RAM es similar al de las memorias flash serie y EEPROM serie. La principal diferencia entre la CY15B104Q y una flash o EEPROM serie con la misma disposición de pines es el rendimiento de escritura superior, la alta resistencia y el bajo consumo de la F-RAM.

Arquitectura de memoria

Al acceder al CY15B104Q, el usuario direcciona 512K posiciones de ocho bits de datos cada una. Estos ocho bits de datos se introducen o extraen en serie. Se accede a las direcciones utilizando el protocolo SPI, que incluye una selección de chip (para permitir múltiples dispositivos en el bus), un opcode y una dirección de tres bytes. Los 5 bits superiores del rango de direcciones son valores "don't care". La dirección completa de 19 bits especifica cada dirección de byte de forma única. La mayoría de las funciones del CY15B104Q están controladas por la interfaz SPI o gestionadas por circuitos integrados. El tiempo de acceso para la operación de memoria es esencialmente cero, más allá del tiempo necesario para el protocolo serie. Es decir, la memoria se lee o escribe a la velocidad del bus SPI. A diferencia de una flash o EEPROM serie, no es necesario sondear el dispositivo para saber si está listo, ya que las escrituras se producen a la velocidad del bus. En el momento en que una nueva transacción de bus puede ser transferida al dispositivo, una operación de escritura se ha completado. Esto se explica con más detalle en la sección de interfaz.