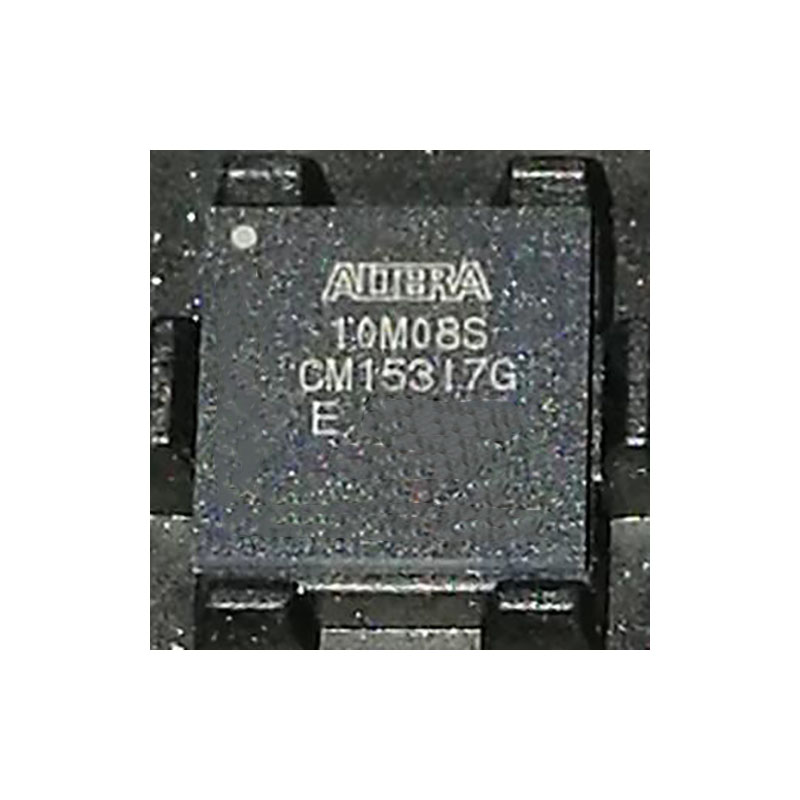

Descripción:

El producto 10M08SCM153I7G pertenece a la serie MAX ® 10 FPGA de INTEL.

Para lograr un bajo consumo de energía estática, la arquitectura estructural central de esta serie adopta una arquitectura de bajo consumo de energía estática, que se basa en la tecnología optimizada de memoria flash de 55 nanómetros.

El producto ofrece flexibilidad e integración, con un único dispositivo que integra memoria flash no volátil, dispositivos lógicos programables (PLD), memoria de acceso aleatorio (RAM), procesamiento digital de señales (DSP), interfaz de memoria externa DDR3, convertidor analógico-digital (ADC), bucle de bloqueo de fase (PLL) y varios estándares de E/S en un pequeño encapsulado de 3 mm x 3 mm.

Con un método de configuración sencillo y rápido, la configuración del dispositivo puede completarse en menos de 10 milisegundos en una memoria flash segura integrada en el chip.

Entre las características más destacadas de los dispositivos Intel MAX 10 se incluyen:

- Flash de configuración dual almacenada internamente

- Memoria flash de usuario

- Asistencia inmediata

- Convertidores analógico-digitales (ADC) integrados

- Compatibilidad con el procesador de núcleo blando Nios II de un chip

Aplicaciones:

El producto es la solución ideal para la gestión de sistemas, la expansión de E/S, los planos de control de comunicaciones y las aplicaciones industriales, de automoción y de consumo.

Principales ventajas de los dispositivos Intel MAX 10

Configuración sencilla y rápida:

La memoria flash segura integrada permite configurar el dispositivo en menos de 10 ms.

Flexibilidad e integración:

Dispositivo único que integra lógica PLD, RAM, memoria flash, procesamiento digital de señales (DSP), ADC, bucle de fase bloqueada (PLL) y E/S.

Paquetes pequeños disponibles a partir de 3 mm × 3 mm

Baja potencia

Modo de espera: reducción significativa de la potencia en espera y reanudación en menos de 1 ms.

Mayor duración de la batería: consumo desde el apagado total en menos de 10 ms.

Ciclo de vida estimado en 20 años

Basada en la tecnología de proceso flash integrada de 55 nm de TSMC

Herramientas de diseño de alta productividad

Edición Intel Quartus® Prime Lite (licencia sin coste)

Herramienta de integración de sistemas Platform Designer (Standard)

DSP Builder para FPGAs Intel

Suite de diseño integrado (EDS) Nios® II

Tecnología

Tecnología de proceso TSMC Embedded Flash (Flash + SRAM) de 55 nm

Embalaje

Paquetes de bajo coste y pequeño factor de forma: admiten múltiples tecnologías de empaquetado y pasos de patillas.

Múltiples densidades de dispositivos con huellas de encapsulado compatibles para una migración sin problemas entre diferentes densidades de dispositivos.

Conformidad con RoHS6

Arquitectura básica

Tabla de consulta (LUT) de 4 entradas y elemento lógico (LE) de registro único

LEs dispuestos en un bloque de matriz lógica (LAB)

RAM integrada y memoria flash de usuario

Relojes y PLL

Bloques multiplicadores integrados

E/S de propósito general

Bloques de memoria interna

Bloques de memoria M9K-9 kilobits (Kb)

Bloques en cascada para crear funciones RAM, de doble puerto y FIFO

Memoria flash de usuario (UFM)

Almacenamiento no volátil accesible al usuario

Frecuencia de funcionamiento a alta velocidad

Gran tamaño de memoria

Alta retención de datos

Opción de varias interfaces

Bloques multiplicadores integrados

Un multiplicador de 18 × 18 o dos de 9 × 9

Bloques en cascada que permiten crear filtros, funciones aritméticas y cadenas de procesamiento de imágenes.

ADC

Tipo de registro de aproximación sucesiva (SAR) de 12 bits

Hasta 17 entradas analógicas

Velocidad acumulada de hasta 1 millón de muestras por segundo ( MSPS)

Capacidad integrada de detección de temperatura

Redes de relojes

Relojes mundiales

Frecuencia de alta velocidad en la red de reloj

Oscilador interno

Oscilador de anillo interno integrado

PLLs

Analógico

Baja inestabilidad

Síntesis de reloj de alta precisión

Compensación del retardo del reloj

Búfer de retardo cero

Múltiples tomas de salida

E/S de propósito general (GPIO)

Compatible con varios estándares de E/S

Terminación en chip (OCT)

Receptor y transmisor LVDS de hasta 720 megabits por segundo (Mbps)

Interfaz de memoria externa (EMIF)

Admite interfaces de memoria externa de hasta 600 Mbps:

DDR3, DDR3L, DDR2, LPDDR2 (en 10M16, 10M25, 10M40 y 10M50.)

SRAM (sólo soporte de hardware)

Nota:

EMIF sólo es compatible con determinadas combinaciones de densidad de dispositivos y paquetes Intel MAX 10. Consulte la Guía del usuario de la interfaz de memoria externa para obtener más información.

Para un rendimiento de 600 Mbps, se requiere un grado de velocidad de dispositivo -6. El desempeño varía según el grado del dispositivo (comercial, industrial o automotriz) y el grado de velocidad del dispositivo (-6 o -7). Consulte la Hoja de datos del dispositivo Intel MAX 10 FPGA o la Calculadora de especificaciones de interfaz de memoria externa para obtener más detalles.

Configuración

Configuración interna

JTAG

Opciones de cifrado y compresión Advanced Encryption Standard (AES) de 128 bits

Retención de datos en memoria flash de 20 años a 85 °C

Sistemas flexibles de suministro eléctrico

Opciones de dispositivo de alimentación simple y doble

Apagado del búfer de entrada controlado dinámicamente

Modo de reposo para una reducción dinámica de la potencia

Opciones de funciones para dispositivos Intel MAX 10

Compacto

Dispositivos con arquitectura de núcleo que presentan una única imagen de configuración con capacidad de autoconfiguración

Flash

Dispositivos con arquitectura de núcleo:

Imagen de configuración dual con capacidad de autoconfiguración

Capacidad de actualización remota del sistema

Inicialización de la memoria

Analógico

Dispositivos con arquitectura de núcleo:

Imagen de configuración dual con capacidad de autoconfiguración

Capacidad de actualización remota del sistema

Inicialización de la memoria

ADC integrado