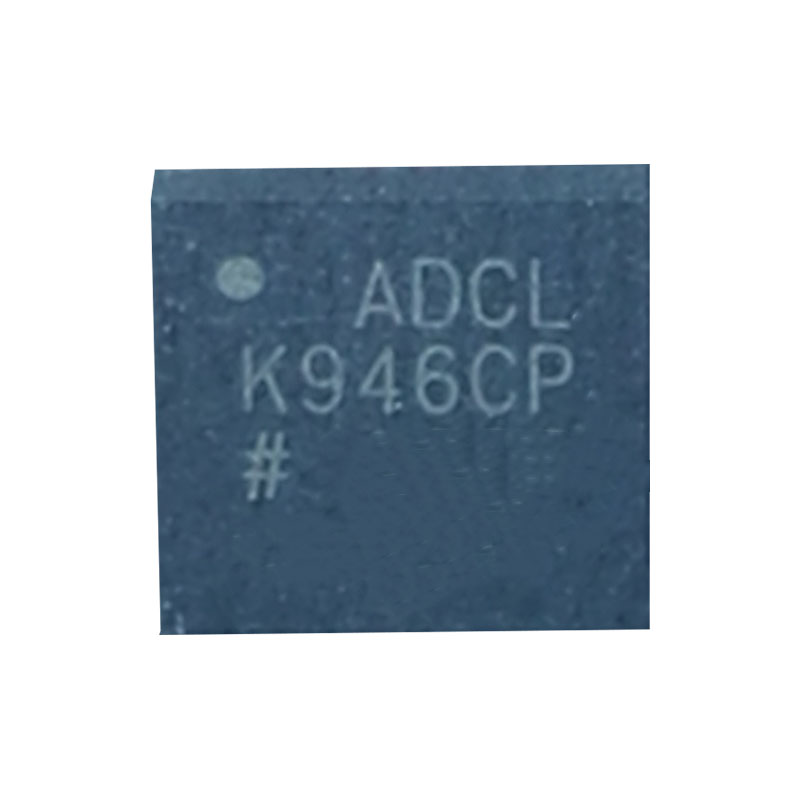

Description :

L'ADCLK946BCPZ est un tampon de sortie d'horloge ultra-rapide fabriqué sur le procédé bipolaire au silicium germanium (SiGe) XFCB3 exclusif d'Analog Devices, Inc. Ce dispositif est conçu pour les applications à haute vitesse nécessitant une faible gigue.

L'appareil possède une entrée différentielle équipée de résistances de terminaison différentielles centrées de 100 Ω sur la puce. L'entrée accepte les entrées LVPECL, CML, 3,3 V CMOS (simple extrémité) couplées en courant continu et les entrées CMOS, LVDS et LVPECL 1,8 V couplées en courant alternatif. Une broche VREF est disponible pour polariser les entrées à couplage alternatif.

L'ADCLK946BCPZ dispose de six pilotes de sortie ECL (logique à émetteurs couplés). Pour un fonctionnement LVPECL (ECL positif), polariser VCC sur l'alimentation positive et VEE sur la masse. Pour le fonctionnement ECL, polariser VCC à la masse et VEE à l'alimentation négative.

Les étages de sortie ECL sont conçus pour piloter directement 800 mV de chaque côté dans 50 Ω terminés à VCC - 2 V pour une excursion de sortie différentielle totale de 1,6 V.

Caractéristiques:

Fréquence de fonctionnement de 4,8 GHz

75 fs rms gigue aléatoire à large bande

Terminaisons d'entrée sur puce

Alimentation 3,3 V

Applications :

Systèmes de communication : stations de base sans fil, systèmes de communication par fibre optique, communication par satellite, etc.

Convertisseur de données : source d'horloge pour les convertisseurs de données à grande vitesse tels que ADC, DAC, etc.

Générateur d'horloge : fournit un signal d'horloge très stable pour le système.

Instrumentation : Instruments tels que les oscilloscopes, les générateurs de signaux, etc. qui nécessitent des sources d'horloge de haute stabilité.

DESCRIPTION FONCTIONNELLE

INPUTS DE CLOCK

L'ADCLK946 accepte une entrée d'horloge différentielle et la distribue aux six sorties LVPECL.

La fréquence maximale spécifiée est le point auquel la tension de sortie est 50% de la tension de sortie standard LVPECL.

L'appareil dispose d'une entrée différentielle équipée de résistances de terminaison différentielles de 100 Ω sur la puce.

L'entrée accepte les entrées LVPECL, CML, CMOS 3,3 V (à terminaison unique) couplées en courant continu et les entrées CMOS 1,8 V, LVDS et LVPECL couplées en courant alternatif.

Une broche VREF est disponible pour polariser les entrées couplées en courant alternatif.

Maintenir la tension différentielle d'entrée d'environ 400 mV p-p à un maximum de 3,4 V p-p. Pour divers schémas de terminaison d'entrée d'horloge.

La gigue de sortie est dégradée par une vitesse de balayage d'entrée inférieure à 1 V/ns.

L'ADCLK946 est spécialement conçu pour minimiser la gigue aléatoire ajoutée sur une large plage de vitesse de balayage d'entrée.

Dans la mesure du possible, les signaux d'entrée trop importants doivent être bridés à l'aide de diodes Schottky rapides, car les atténuateurs réduisent la vitesse de balayage.

Les signaux d'entrée de plus de quelques centimètres doivent être acheminés par des diélectriques à faible perte ou des câbles présentant de bonnes caractéristiques à haute fréquence.

SORTIES DE CLOCK

Les performances spécifiées nécessitent l'utilisation de terminaisons appropriées pour les lignes de transmission.

Les sorties LVPECL de l'ADCLK946 sont conçues pour piloter directement 800 mV dans un câble de 50 Ω ou dans des lignes de transmission microstrip/stripline terminées par 50 Ω référencés à VCC - 2 V.

Les sorties sont conçues pour une meilleure adaptation à la ligne de transmission.

Si les signaux à grande vitesse doivent être acheminés sur plus d'un centimètre, la technique de la microruban ou de la stripline est nécessaire pour garantir des temps de transition corrects et pour éviter un anneau de sortie excessif et une dispersion du temps de propagation dépendant de la largeur d'impulsion.

La terminaison équivalente à celle de Thevenin utilise un réseau de résistances pour fournir une terminaison de 50 Ω à une tension continue qui est inférieure à VOL du pilote LVPECL. Dans ce cas, VS_DRV sur l'ADCLK946 doit être égal à VCC du tampon de réception. Bien que la combinaison de résistances illustrée à la figure 15 donne un point de polarisation en courant continu de VS_DRV - 2 V, la tension en mode commun réelle est VS_DRV - 1,3 V car il y a un courant supplémentaire qui circule à partir du circuit d'alimentation de l'ADCLK946.

ADCLK946 LVPECL driver through the pull-down resistor. La terminaison LVPECL en Y est un schéma de terminaison élégant qui utilise le moins de composants possible et offre une adaptation d'impédance en mode pair et impair. L'adaptation d'impédance en mode pair est une considération importante pour les lignes de transmission étroitement couplées à haute fréquence. Son principal inconvénient est qu'elle offre une flexibilité limitée pour varier la force d'entraînement du circuit d'attaque LVPECL émetteur-suiveur. Ceci peut être une considération importante lors du pilotage de grandes longueurs de lignes, mais n'est généralement pas un problème.