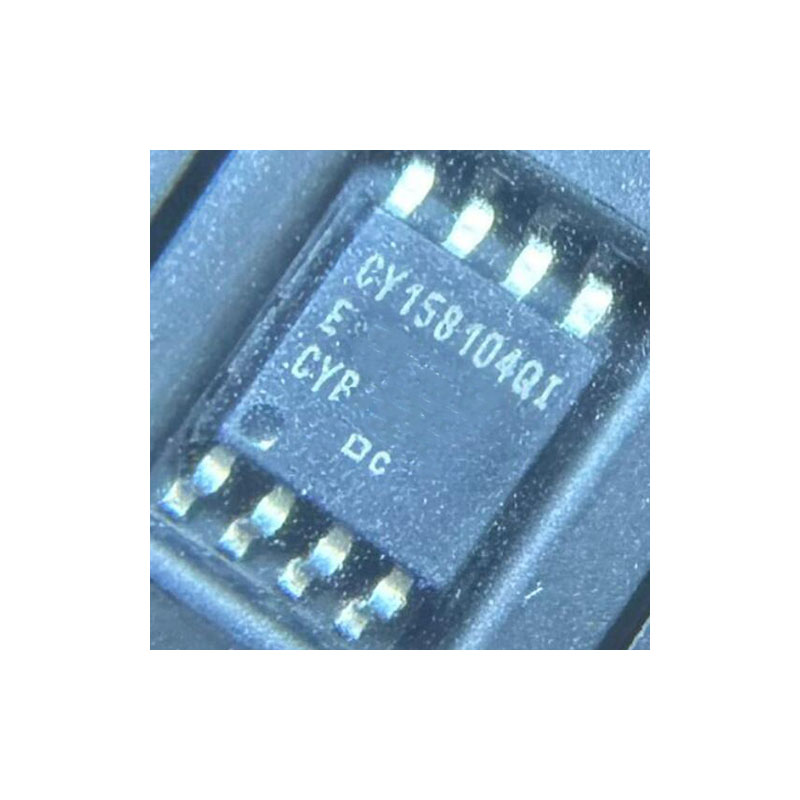

Description :

Le CY15B104Q est une mémoire non volatile de 4 Mbits utilisant un processus ferroélectrique avancé. Une mémoire vive ferroélectrique ou F-RAM est non volatile et effectue des lectures et des écritures similaires à celles d'une RAM. Elle permet une rétention fiable des données pendant 151 ans tout en éliminant les complexités, les frais généraux et les problèmes de fiabilité au niveau du système causés par les mémoires flash série, EEPROM et autres mémoires non volatiles.

Contrairement à la flash série et à l'EEPROM, CY15B104Q effectue les opérations d'écriture à la vitesse du bus. Il n'y a pas de délai d'écriture. Les données sont écrites dans la matrice de mémoire immédiatement après que chaque octet a été transféré avec succès dans le dispositif. Le cycle de bus suivant peut commencer sans qu'il soit nécessaire d'interroger les données. En outre, le produit offre une endurance d'écriture substantielle par rapport à d'autres mémoires non volatiles. Le CY15B104Q est capable de supporter 1014 cycles de lecture/écriture, soit 100 millions de fois plus de cycles d'écriture que l'EEPROM.

Ces capacités font du CY15B104Q la solution idéale pour les applications de mémoire non volatile nécessitant des écritures fréquentes ou rapides. Les exemples vont de la collecte de données, où le nombre de cycles d'écriture peut être critique, aux contrôles industriels exigeants où le long temps d'écriture de la flash série ou de l'EEPROM peut entraîner la perte de données.

Le CY15B104Q offre des avantages substantiels aux utilisateurs d'EEPROM série ou de flash en tant que remplacement matériel. Le CY15B104Q utilise le bus SPI à grande vitesse, qui améliore la capacité d'écriture à grande vitesse de la technologie F-RAM. Le dispositif incorpore un Device ID en lecture seule qui permet à l'hôte de déterminer le fabricant, la densité du produit et la révision du produit. Les spécifications du dispositif sont garanties sur une plage de température industrielle de -40 °C à +85 °C.

Caractéristiques:

Mémoire ferroélectrique à accès aléatoire (F-RAM) de 4 Mbits organisée logiquement en 512 K × 8

Haute endurance 100 billions (1014) de lectures/écritures

Conservation des données pendant 151 ans

NoDelay™ écrit

Procédé ferroélectrique avancé à haute fiabilité

Interface périphérique série (SPI) très rapide

Fréquence jusqu'à 40 MHz

Remplacement matériel direct de la flash série et de l'EEPROM

Prend en charge le mode SPI 0 (0, 0) et le mode 3 (1, 1)

Système sophistiqué de protection contre l'écriture

Protection matérielle à l'aide de la broche de protection contre l'écriture (WP)

Protection logicielle à l'aide de l'instruction Write Disable

Protection par bloc logiciel pour 1/4, 1/2 ou l'ensemble de la matrice

ID du fabricant et ID du produit

Faible consommation d'énergie

300 mA courant actif à 1 MHz

100 mA (typ) courant de veille

3 mA (typ) courant en mode veille

Fonctionnement à basse tension : VDD = 2,0 V à 3,6 V

Température industrielle : -40 °C à +85 °C

Conforme à la directive sur la limitation des substances dangereuses (RoHS)

Applications :

Un tout nouveau mode de vie et une nouvelle expérience de la santé pour le citoyen connecté d'aujourd'hui

Electronique grand public

Applications spatiales

Vue d'ensemble

Le CY15B104Q est une mémoire F-RAM série. La matrice de mémoire est organisée logiquement en 524 288 × 8 bits et est accessible par un bus d'interface périphérique série (SPI) standard. Le fonctionnement de la F-RAM est similaire à celui des mémoires flash et EEPROM sérielles. La principale différence entre CY15B104Q et une flash ou une EEPROM série ayant le même brochage est la performance d'écriture supérieure de la F-RAM, sa grande endurance et sa faible consommation d'énergie.

Architecture de la mémoire

Lors de l'accès au CY15B104Q, l'utilisateur adresse 512K emplacements de huit bits de données chacun. Ces huit bits de données sont décalés vers l'intérieur ou vers l'extérieur en série. L'accès aux adresses se fait à l'aide du protocole SPI, qui comprend une sélection de puce (pour permettre la présence de plusieurs appareils sur le bus), un code d'opération et une adresse de trois octets. Les 5 bits supérieurs de la plage d'adresses sont des valeurs "sans importance". L'adresse complète de 19 bits spécifie chaque adresse d'octet de manière unique. La plupart des fonctions du CY15B104Q sont soit contrôlées par l'interface SPI, soit gérées par des circuits intégrés. Le temps d'accès à la mémoire est pratiquement nul, au-delà du temps nécessaire au protocole série. En d'autres termes, la mémoire est lue ou écrite à la vitesse du bus SPI. Contrairement à une mémoire flash ou EEPROM série, il n'est pas nécessaire d'interroger le dispositif pour savoir s'il est prêt, car les écritures se font à la vitesse du bus. Une opération d'écriture est terminée lorsqu'une nouvelle transaction de bus peut être transférée dans l'appareil. Ce point est expliqué plus en détail dans la section relative à l'interface.