Description :

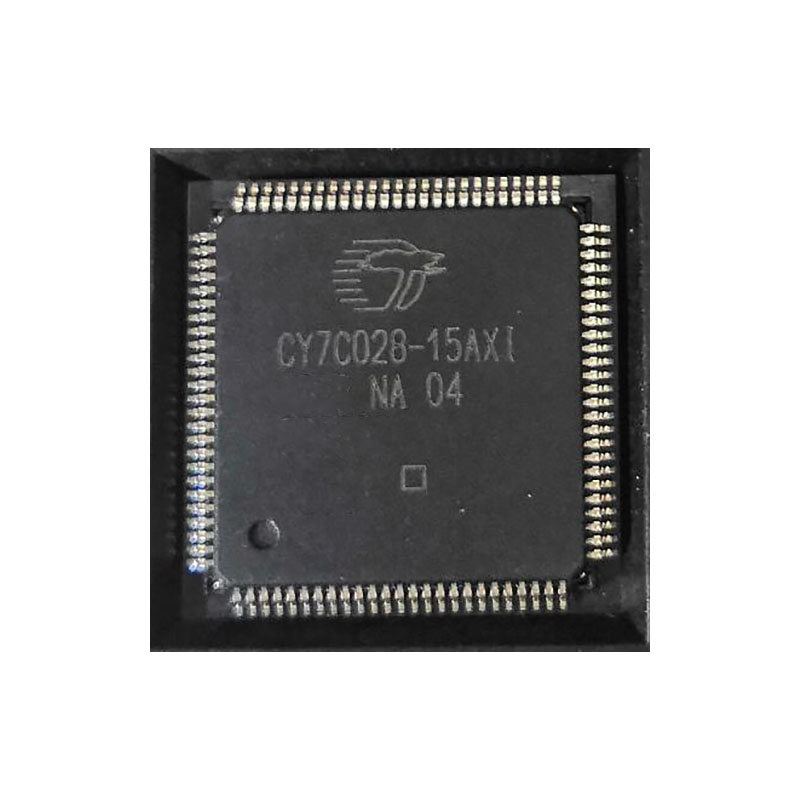

Les CY7C027 et CY7C028 sont des RAM statiques CMOS 32K, 64K × 16 à double port et à faible consommation d'énergie. Divers schémas d'arbitrage sont inclus dans les dispositifs pour gérer les situations où plusieurs processeurs accèdent au même morceau de données. Deux ports sont fournis, permettant un accès indépendant et asynchrone pour les lectures et les écritures à n'importe quel endroit de la mémoire. Les dispositifs peuvent être utilisés comme des RAM statiques autonomes de 16 bits à double port ou plusieurs dispositifs peuvent être combinés pour fonctionner comme une RAM statique maître/esclave à double port de 32 bits ou plus. Une broche M/S est fournie pour mettre en œuvre des applications de mémoire 32 bits ou plus sans avoir besoin de dispositifs maître et esclave séparés ou d'une logique discrète supplémentaire. Les domaines d'application comprennent les conceptions interprocesseurs et multiprocesseurs, la mise en mémoire tampon de l'état des communications et la mémoire vidéo/graphique à double port.

Chaque port possède des broches de contrôle indépendantes : double validation de puce (CE0 et CE1), validation de lecture ou d'écriture (R/W) et validation de sortie (OE). Deux indicateurs sont fournis sur chaque port (BUSY et INT). BUSY signale que le port essaie d'accéder à l'emplacement auquel l'autre port accède actuellement. Le drapeau d'interruption (INT) permet la communication entre les ports ou les systèmes au moyen d'une boîte aux lettres. Les sémaphores sont utilisés pour transmettre un drapeau, ou jeton, d'un port à l'autre afin d'indiquer qu'une ressource partagée est en cours d'utilisation. La logique du sémaphore est composée de huit verrous partagés. Un seul côté peut contrôler le verrou (sémaphore) à tout moment. Le contrôle d'un sémaphore indique qu'une ressource partagée est en cours d'utilisation. Une fonction de mise hors tension automatique est contrôlée indépendamment sur chaque port par les broches d'activation de puce

Les CY7C027 et CY7C028 sont disponibles en boîtiers TQFP (Thin Quad Flat Pack) de 100 broches.

Les CY7C027 et CY7C028 sont Obsolète

Caractéristiques:

Véritables cellules de mémoire à double port qui permettent l'accès simultané au même emplacement de mémoire

Organisation 64K × 16 (CY7C028)

CMOS 0,35 micron pour une vitesse et une puissance optimales

Accès à grande vitesse : 15 et 20 ns

Faible puissance de fonctionnement

Actif : ICC = 180 mA (typique)

En veille : ISB3 = 0,05 mA (typique)

Fonctionnement entièrement asynchrone

Mise hors tension automatique

Bus de données extensible à 32 bits ou plus grâce à la sélection de puce maître/esclave en cas d'utilisation de plus d'un appareil

Logique d'arbitrage sur puce

Sémaphores inclus pour permettre l'échange logiciel entre les ports

Indicateurs INT pour la communication de port à port

Contrôle séparé de l'octet supérieur et de l'octet inférieur

La double puce permet

Sélection des broches pour maître ou esclave

Gammes de températures commerciales et industrielles

Disponible en TQFP 100 broches

Paquets sans plomb disponibles

Mode de conservation des données :

Les CY7C027 et CY7C028 ont été conçus en tenant compte de la sauvegarde par batterie. La tension de rétention des données et le courant d'alimentation sont garantis en fonction de la température. Les règles suivantes assurent la conservation des données :

- L'activation de la puce (CE) doit être maintenue à un niveau élevé pendant la conservation des données, entre VCC et VCC - 0,2 V.

- CE doit être maintenu entre VCC - 0,2 V et 70% de VCC pendant les transitions de mise sous tension et de mise hors tension.

- La RAM peut commencer à fonctionner > tRC après que VCC ait atteint la tension minimale de fonctionnement (4,5 V).

NOTES :

Test initial et après toute modification de la conception ou du processus susceptible d'affecter ces paramètres

CE = VCC, VIN = GND à VCC, TA = 25 °C. Ce paramètre est garanti mais non testé.

Architecture :

Les CY7C027 et CY7C028 sont constitués d'une matrice de 32K et 64K mots de 16 bits chacun de cellules RAM à double port, de lignes d'E/S et d'adresse, et de signaux de contrôle (CE, OE, R/W). Ces broches de contrôle permettent un accès indépendant pour la lecture ou l'écriture à n'importe quel endroit de la mémoire. Pour gérer les lectures/écritures simultanées au même endroit, une broche BUSY est fournie sur chaque port. Deux broches d'interruption (INT) peuvent être utilisées pour la communication de port à port. Deux broches de contrôle de sémaphore (SEM) sont utilisées pour allouer des ressources partagées. Avec la broche M/S, les appareils peuvent fonctionner en tant que maître (les broches BUSY sont des sorties) ou en tant qu'esclave (les broches BUSY sont des entrées). Les appareils disposent également d'une fonction de mise hors tension automatique contrôlée par CE. Chaque port est doté de sa propre commande d'activation de sortie (OE), qui permet de lire les données du dispositif.