説明

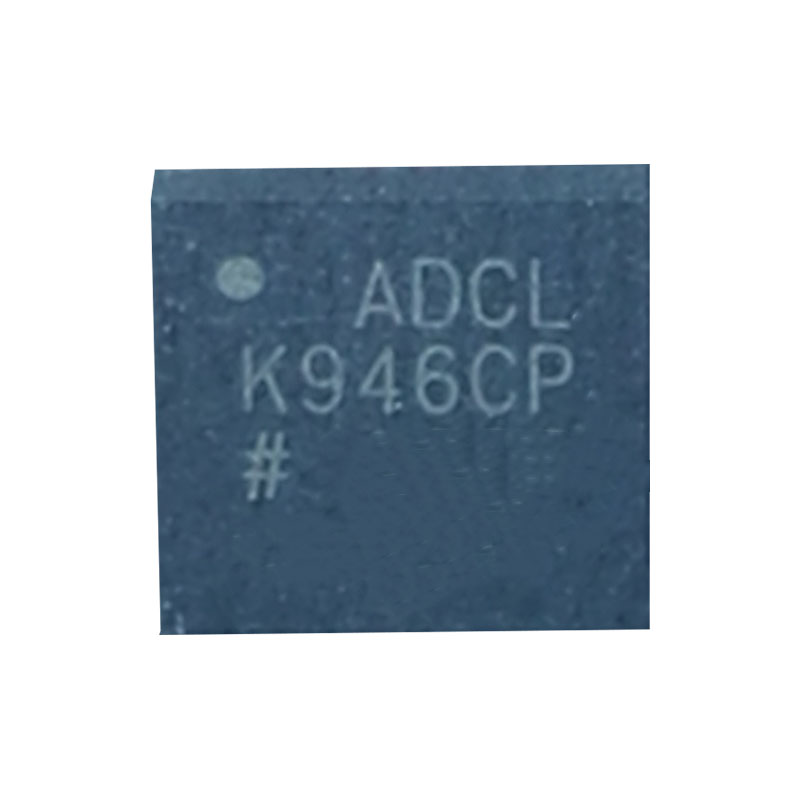

ADCLK946BCPZは、アナログ・デバイセズ社独自のXFCB3シリコン・ゲルマニウム(SiGe)バイポーラ・プロセスで製造された超高速クロック・ファンアウト・バッファです。このデバイスは、低ジッタを必要とする高速アプリケーション向けに設計されています。

このデバイスは、センタータップされた差動、100Ωのオンチップ終端抵抗を備えた差動入力を備えています。入力は、直流結合の LVPECL、CML、3.3 V CMOS(シングルエンド)、および交流結合の 1.8 V CMOS、LVDS、LVPECL 入力に対応しています。VREFピンは、交流結合入力のバイアス用に使用できます。

ADCLK946BCPZ は 6 つのフルスイング・エミッタ結合ロジック(ECL) 出力ドライバを備えています。LVPECL(正 ECL)動作では、VCC を正電源に、VEE をグランドにバイアスします。ECL動作では、VCCをグランドに、VEEを負電源にバイアスします。

ECL出力段は、VCC - 2 Vに終端された50Ωに各側800 mVを直接駆動するように設計されており、合計1.6 Vの差動出力スイングを持つ。

特徴

4.8 GHz動作周波数

75fs rms広帯域ランダムジッター

オンチップ入力終端

3.3V電源

アプリケーション

通信システム:無線基地局、光ファイバー通信システム、衛星通信など

データ・コンバータ:ADC、DACなどの高速データ・コンバータ用クロック・ソース。

クロック・ジェネレーター:システムに安定性の高いクロック信号を供給する。

計測機器:オシロスコープ、信号発生器など、高安定のタイミング・クロック源を必要とする機器。

機能説明

クロック入力

ADCLK946 は差動クロック入力を受け入れ、それを 6 つの LVPECL 出力すべてに分配します。

最大規定周波数は、出力電圧スイングが標準LVPECLスイングの50%となるポイントである。

このデバイスは、センタータップ差動100Ωオンチップ終端抵抗を備えた差動入力を持っています。

入力は、 直流結合の LVPECL、CML、3.3 V CMOS(シングルエンド)、および交流結合の 1.8 V CMOS、LVDS、LVPECL 入力に対応する。

VREF ピンは、AC 結合入力をバイアスするために使用できる。

差動入力電圧スイングを約400mV p-pから3.4V p-p以下に維持する。

出力ジッター性能は、1 V/ns以下の入力スルーレートで劣化する。

ADCLK946 は、広い入力スルー・レート範囲にわたって、付加されるランダム・ジッタを最小化するように特別に設計されています。

減衰器はスルーレートを低下させるので、可能な限り、高速ショットキーダイオードで過度に大きな入力信号をクランプする。

数センチ以上の入力信号の引き回しは、低損失の誘電体または高周波特性の良いケーブルを使用する。

クロック出力

指定された性能は、適切な伝送ライン終端を使用する必要があります。

ADCLK946 の LVPECL 出力は、VCC - 2 V を基準に 50 Ω で終端された 50 Ω ケーブル又はマイクロストリップ/ストリップライン伝送線路に 800 mV を直接駆動するように設計されている。

出力は最良の伝送線路マッチングが得られるように設計されている。

高速信号を1センチ以上配線する必要がある場合、適切な遷移時間を確保し、過度の出力リンギングやパルス幅依存の伝搬遅延分散を防ぐために、マイクロストリップかストリップライン技術のいずれかが必要となる。

ベニン等価終端は、LVPECL ドライバの VOL より低い直流電圧に 50 Ω終端する抵抗ネットワークを使用する。この場合、ADCLK946 の VS_DRV は受信バッファーの VCC と等しくなければならない。図 15 に示す抵抗の組み合わせでは、直流バイアス点は VS_DRV - 2 V になるが、実際のコモンモード電圧は VS_DRV - 1.3 V である。

ADCLK946 はプルダウン抵抗を通して LVPECL ドライバを接続します。LVPECL Y 終端は、最も少ない部品で、奇数モードと偶数モードのイン ピーダンス・マッチングを提供するエレガントな終端方式です。偶数モードのインピーダンス・マッチングは、高周波で密に結合された伝送線路にとって重要な考慮事項である。その主な欠点は、エミッタフォロワLVPECLドライバの駆動強度を変える柔軟性が限られていることである。これは、長いトレースを駆動する場合に重要な考慮事項になり得るが、通常は問題にならない。