説明

サイプレスのCY14B104Mは、モノリシック集積回路に4Mビットの不揮発性スタティックRAM(nvSRAM)とフル機能のRTCを組み合わせています。内蔵の不揮発性素子にはQuantumTrap技術が採用されており、世界で最も信頼性の高い不揮発性メモリを実現している。SRAMは無制限に読み書きが可能で、独立した不揮発性データは不揮発性素子に保存される。

RTC機能は、うるう年トラッキングとプログラム可能な高精度オシレーターを備えた正確なクロックを提供します。アラーム機能は、定期的な分、時、日、月のアラームをプログラム可能です。プロセス制御用のプログラム可能なウォッチドッグ・タイマーもあります。

CY14B104M nvSRAMは、同じ物理セル内に対になった2つの機能部品で構成されている。SRAM メモリ・セルと不揮発性 QuantumTrap セルである。SRAM メモリ・セルは、標準的な高速スタティック RAM として動作する。SRAMのデータは不揮発性セルに転送され(STORE動作)、あるいは不揮発性セルからSRAMに転送される(RECALL動作)。このユニークなアーキテクチャを使用すると、すべてのセルが並列に記憶され、呼び出される。STORE動作とRECALL動作の間、SRAMの読み出しと書き込みは禁止されます。CY14B104Mは、一般的なSRAMと同様に、無限の読み出しと書き込みをサポートしています。さらに、不揮発性セルからの無限のRECALL動作と最大100万回のSTORE動作が可能です。

特徴

アクセス・タイム 25 ns および 45 ns

内部構成は256K×16

小さなコンデンサーでパワーダウン時にハンズオフ自動STORE

QuantumTrap不揮発性素子へのSTOREは、ソフトウェア、デバイス・ピン、またはパワーダウン時 のAutoStoreによって開始される。

SRAMへのRECALLは、ソフトウェアまたは電源投入により開始される。

高い信頼性

無限の読み取り、書き込み、RECALLサイクル

QuantumTrapへの100万回のSTOREサイクル

20年間のデータ保持

シングル 3 V +20%、-10% 動作

サイプレスnvSRAMのデータ・インテグリティとフル機能のリアルタイム・クロック(RTC)の組み合わせ

ウォッチドッグ・タイマー

プログラム可能な割り込み機能付き時計アラーム

RTC用コンデンサまたはバッテリバックアップ

工業用温度

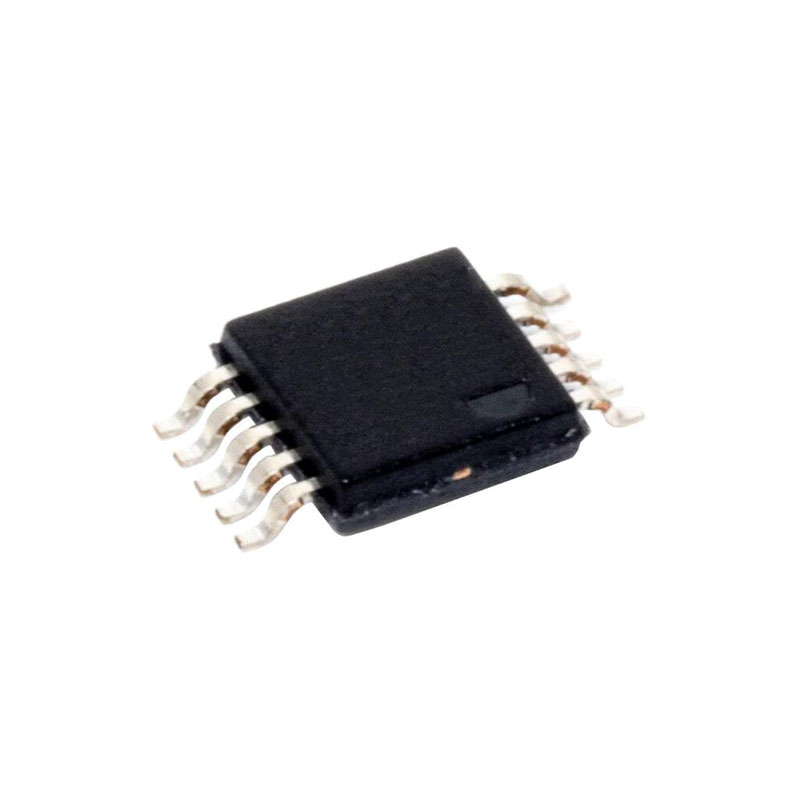

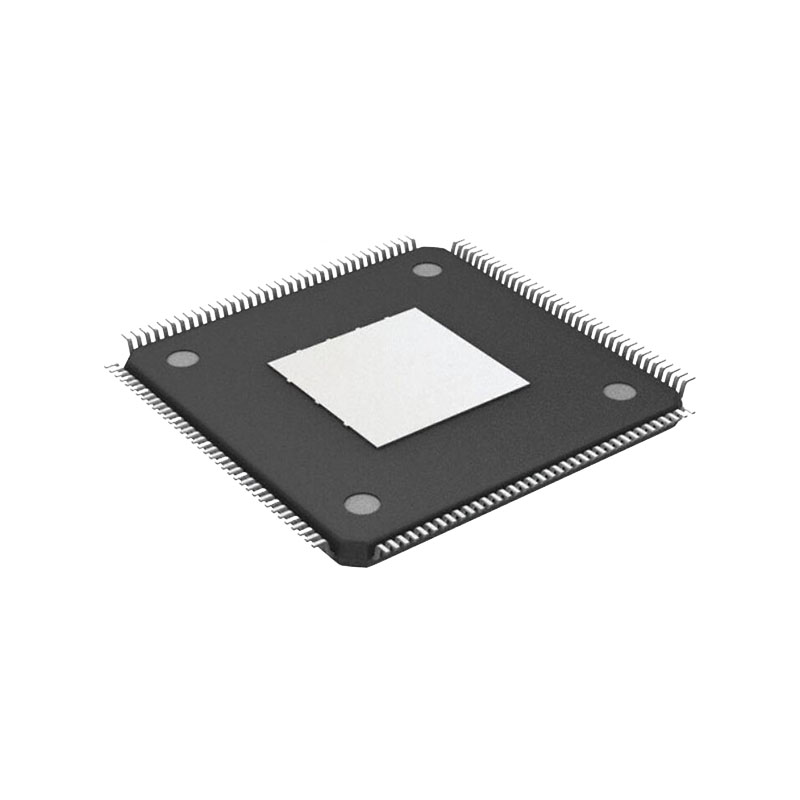

44 ピンおよび 54 ピン TSOP タイプ II

鉛フリーおよび有害物質規制(RoHS)対応

デバイス操作

CY14B104K/CY14B104M nvSRAMは、同じ物理セル内に対をなす2つの機能部品で構成されている。これらは、SRAM メモリ・セルと不揮発性 QuantumTrap セルです。SRAM メモリ・セルは、標準的な高速スタティック RAM として動作する。SRAMのデータは不揮発性セルに転送され(STORE動作)、あるいは不揮発性セルからSRAMに転送される(RECALL動作)。このユニークなアーキテクチャを使用すると、すべてのセルが並列に保存され、呼び出される。STORE動作とRECALL動作の間、SRAMの読み出しと書き込みは禁止される。CY14B104K/CY14B104Mは、一般的なSRAMと同様に、無限の読み出しと書き込みをサポートします。さらに、不揮発性セルからの無限のRECALL動作と最大100万回のSTORE動作が可能です。読み出しと書き込みモードの完全な説明については、25ページのSRAM動作の真理値表を参照してください。

SRAMリード

CY14B104K/CY14B104Mは、CEとOEがLOWで、WEとHSBがHIGHのとき、読み出しサイクルを実行します。ピンA0-18またはA0-17で指定されたアドレスによって、各16ビットの524,288データ・バイトまたは262,144ワードのどれにアクセスするかが決まります。バイト・イネーブル(BHE、BLE)は、16ビット・ワードの場合、どのバイトが出力にイネーブルされるかを決定します。読み出 し がア ド レ ス遷移に よ っ て開始 さ れ る 場合、 出力はtAA (読み出 し サイ クル1) の遅延後に有効にな り ます。CE ま たはOE に よ っ て読み出 し が開始 さ れ る 場合、 出力はtACE ま たはtDOE のいずれか遅い時点で有効にな り ます(読み出 し サイ クル2)。データ出力は、制御入力ピンの遷移を必要とせず、tAA アクセス時間内のアドレス変更に繰り返し応答します。これは、アドレスが再度変更されるか、CE またはOE がHIGH になるか、WE またはHSB がLOW になるまで有効である。

SRAMライト

書き込みサイクルはCEとWEがLOWでHSBがHIGHの時に実行される。アドレス入力は、書き込みサイクルに入る前に安定していなければならず、サイクル終了時にCEまたはWEがHIGHになるまで安定していなければならない。コモンI/OピンDO0-15のデータは、WE制御の書き込み終了前またはCE制御の書き込み終了前に有効なtSDであればメモリに書き込まれる。バイト・イネーブル入力(BHE、BLE)は、16 ビット・ワードの場合、どのバイトが書き込まれるかを決定する。共通I/Oラインのデータ・バス競合を避けるため、書き込みサイクル中はOEをHIGHに保つことを推奨する。OEがLOWのままだと、WEがLOWになった後、内部回路が出力バッファをtHZWEターンオフする。