説明

CY7C027およびCY7C028は、低消費電力のCMOS 32K、64K×16デュアル・ポート・スタティックRAMです。複数のプロセッサが同じデータにアクセスする場合に対応するため、デバイスにはさまざまなアービトレーション方式が搭載されています。2つのポートが提供され、メモリ内の任意の位置への読み出しと書き込みのための独立した非同期アクセスが可能です。このデバイスは、スタンドアロンの16ビット・デュアル・ポート・スタティックRAMとして使用することも、複数のデバイスを組み合わせて32ビット以上のマスタ/スレーブ・デュアル・ポート・スタティックRAMとして機能させることもできます。M/Sピンが用意されているため、マスタ・デバイスとスレーブ・デバイスを別々に用意したり、ディスクリート・ロジックを追加したりすることなく、32ビット以上のメモリ・アプリケーションを実装できます。応用分野には、プロセッサ間およびマルチプロセッサ設計、通信ステータス・バッファリング、デュアル・ポート・ビデオ/グラフィックス・メモリなどがあります。

各ポートには、デュアル・チップ・イネーブル(CE0 と CE1)、リード/ライト・イネーブル(R/W)、出力イネーブル(OE) という独立した制御ピンがある。各ポートには2つのフラグ(BUSYとINT)がある。BUSYは、そのポートが他のポートによってアクセスされているのと同じ場所にアクセスしようとしていることを示します。割り込みフラグ(INT)は、メールボックスによってポート間またはシステム間の通信を許可します。セマフォは、共有リソースが使用中であることを示すために、一方のポートから他方のポートへフラグ(トークン)を渡すために使用されます。セマフォ・ロジックは8つの共有ラッチで構成されている。ラッチ(セマフォ)を制御できるのは常に片側だけです。セマフォの制御は、共有リソースが使用中であることを示します。自動パワーダウン機能は、チップ・イネーブル・ピンによって各ポートで独立して制御されます。

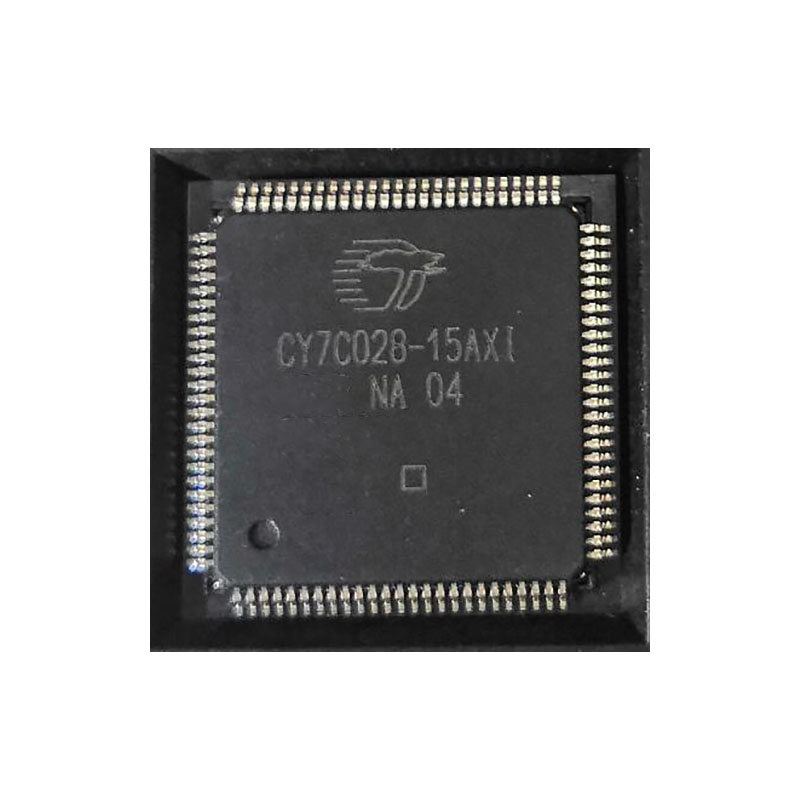

CY7C027およびCY7C028は、100ピンのTQFP(Thin Quad Flat Pack)パッケージで提供される。

CY7C027とCY7C028は 廃止

特徴:

同じメモリ位置への同時アクセスを可能にする真のデュアルポート・メモリセル

64K×16 構成(CY7C028)

0.35ミクロンCMOSで最適なスピードとパワーを実現

高速アクセス:15および20ナノ秒

低動作電力

アクティブICC = 180 mA(代表値)

スタンバイ: ISB3 = 0.05 mA(代表値)

完全な非同期動作

自動パワーダウン

複数のデバイスを使用する場合、マスター/スレーブ・チップ・セレクトを使用してデータ・バスを32ビット以上に拡張可能

オンチップ・アービトレーション・ロジック

ポート間のソフトウェアハンドシェイクを可能にするセマフォを搭載

ポート間通信用INTフラグ

上位バイトと下位バイトの分離制御

デュアルチップ

マスターまたはスレーブのピン選択

商業用および工業用温度範囲

100ピンTQFPで入手可能

鉛フリーパッケージあり

データ保持モード:

CY7C027およびCY7C028は、バッテリー・バックアップを念頭に設計されています。データ保持電圧と供給電流は温度に対して保証されています。以下のルールによりデータ保持を保証します:

- チップイネーブル(CE)は、データ保持中、VCC~VCC - 0.2 Vの範囲でHIGHに保持する必要がある。

- CEはパワーアップ、パワーダウンの遷移中、VCC - 0.2 VからVCCの70%の間に保たれなければならない。

- RAMは、VCCが最低動作電圧(4.5V)に達した後、>tRCで動作を開始することができる。

注意事項

これらのパラメータに影響を与える可能性のある設計または工程の変更後、初期にテストされる。

CE = VCC、VIN = GND to VCC、TA = 25 °C。本パラメータは保証値であり、テスト値ではありません。

建築:

CY7C027とCY7C028は、各16ビットの32Kワードと64Kワードのデュアル・ポートRAMセル、I/Oライン、アドレス・ライン、制御信号(CE、OE、R/W)のアレイで構成されています。これらの制御ピンは、メモリ内の任意の位置への読み出しまたは書き込みのための独立したアクセスを可能にします。同じ場所への同時書き込み/読み出しに対応するため、BUSYピンが各ポートに用意されています。2つの割り込み(INT)ピンはポート間通信に使用できます。2つのセマフォ(SEM)制御ピンは、共有リソースの割り当てに使用されます。M/Sピンにより、デバイスはマスタ(BUSYピンは出力)またはスレーブ(BUSYピンは入力)として機能します。また、CEによって制御される自動パワーダウン機能も備えています。各ポートは独自の出力イネーブル制御(OE)を備えており、デバイスからデータを読み出すことができます。