説明

CY7C1471V33は、3.3V、2M×36の同期フロースルー・バーストSRAMであり、ウェイト・ステートを挿入することなく、無制限の真のバック・トゥ・バック読み出しまたは書き込み動作をサポートするように特別に設計されています。CY7C1471V33は、先進の

NoBL(ノー・バス・レイテンシー)ロジックは、毎クロック・サイクルでデータを転送し、連続した読み出しまたは書き込み動作を可能にするために必要です。この機能により、特に頻繁な書き込み/読み出し遷移を必要とするシステムにおいて、SRAMを介したデータのスループットが劇的に向上します。

すべての同期入力は、クロックの立ち上がりエッジによって制御される入力レジスタを通過する。クロックはクロック入力イネーブル(CEN)信号を修飾し、この信号がディアサートされると動作が一時停止し、前のクロック・サイクルが延長される。クロックの立ち上がりからの最大アクセス遅延は6.5ns(133MHzデバイス)である。

書き込み動作は、2 バイトまたは 4 バイトのライトセレクト(BWX)とライトイネーブル(WE)入力によって制御される。すべての書き込みは、オンチップ同期セルフタイミング書き込み回路で行われる。

3つの同期チップ・イネーブル(CE1、CE2、CE3)と非同期出力イネーブル(OE)により、バンク選択と出力トライステート制御が簡単に行えます。バスの競合を避けるため、書き込みシーケンスのデータ部分では、出力ドライバは同期的にトライステートされます。

特徴

No Bus Latency™ (NoBL™)アーキテクチャは、書き込みサイクルと読み出しサイクルの間のデッドサイクルを排除します。

ゼロ・ウェイト・ステートで最大133MHzのバス動作をサポート。

データは1クロックごとに転送される。

ピン互換性があり、機能的にはZBT™デバイスと同等

OEを使用する必要のない、内部セルフ・タイミング出力バッファ・コントロール

フロースルー動作用登録入力

バイト書き込み機能

3.3 V/2.5 V I/O電源(VDDQ)

クロックから出力までの時間が速い

6.5 ns(133MHzデバイスの場合)

クロックイネーブル(CEN)端子で、クロックとサスペンド動作を有効にする。

同期自己タイミング書き込み

非同期出力イネーブル(OE)

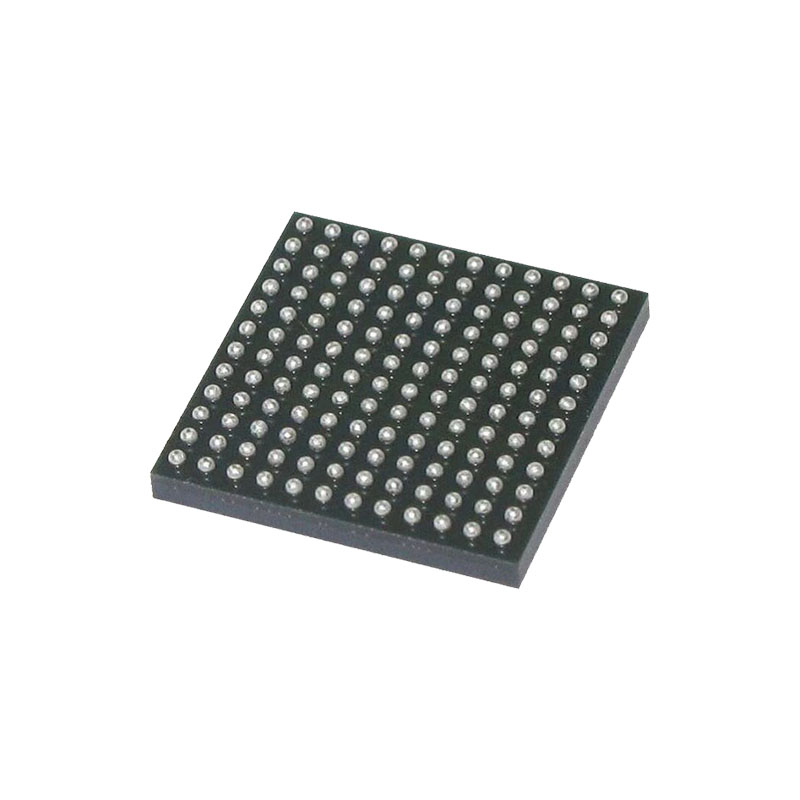

CY7C1471V33 は、JEDEC 規格の鉛フリー 100 ピン TQFP で提供される。

3つのチップイネーブル(CE1、CE2、CE3)により、奥行きを簡単に拡張可能

ZZモードまたはCE非選択で自動パワーダウン機能が利用可能

バースト機能-リニアまたはインターリーブ・バースト・オーダー

低い待機電力

機能概要

CY7C1471V33は、書き込み-読み出し遷移中の待機状態をなくすように設計された、同期フロースルー・バーストSRAMです。すべての同期入力は、クロックの立ち上がりエッジによって制御される入力レジスタを通過します。クロック信号は、クロックイネーブル入力信号(CEN)で修飾されます。CENがHIGHの場合、クロック信号は認識されず、すべての内部状態が維持される。すべての同期動作はCENで修飾される。クロック立ち上がりからの最大アクセス遅延(tCDV)は6.5ns(133MHzデバイス)である。アクセスは、クロックの立ち上がりエッジで3つのチップ・イネーブル(CE1、CE2、CE3)をすべてアクティブにすることで開始できる。(CEN)がアクティブLOWでADV/LDがアサートLOWの場合、デバイスに提示されたアドレスがラッチされる。書き込みイネーブル(WE)の状態により、アクセスは読み出しまたは書き込みのいずれかとなる。バイト・ライト・セレクト(BWX)は、バイト・ライト動作に使用できる。書き込み動作は、ライト・イネーブル(WE)によって制限される。すべての書き込みは、オンチップ同期自己タイミング書き込み回路によって簡素化される。3つの同期チップ・イネーブル(CE1、CE2、CE3)と非同期出力イネーブル(OE)により、深度拡張が簡素化される。すべての動作(読み出し、書き込み、選択解除)はパイプライン化されている。ADV/LDは、デバイスが選択解除された後、次の動作のために新しいアドレスをロードするためにLOW駆動されなければならない。

シングル・リード・アクセス

クロック立ち上がり時に以下の条件が満たされると、読み出しアクセスが開始される:CE1、CE2、CE3 がすべてアクティブにアサートされている。WEがHIGHにデアサートされている。ADV/LDはLOWとしてアサートされる。アドレス入力に示されたアドレスはアドレス・レジスタにラッチされ、メモリ・アレイと制御ロジッ クに示される。制御ロジッ クは、 読み出 し ア ク セ ス が進行中であ る こ と を判断 し 、 要求 さ れたデー タ が出力バ ッ フ ァ に伝搬 さ れ る よ う に し ます。OE がア ク テ ィ ブLOW であれば、 デー タ は6.5ns (133MHz デバ イ ス) 以内に利用可能 と な り ます。読み出 し ア ク セ ス の最初の ク ロ ッ ク の後、 出力バ ッ フ ァ ーはOE と 内部制御 ロ ジ ッ ク に よ っ て制御 さ れます。要求 さ れたデー タ を出力す る には、OE をLOW に駆動す る 必要があ り ます。続くクロックで、別の動作(読み出し/書き込み/選択解除)を開始することができる。チップイネーブル信号の1つによってクロック立ち上がり時にSRAMが選択解除されると、出力は直ちに3ステートされる。

バースト・リード・アクセス

CY7C1471V33 にはバースト・カウンタが内蔵されており、アドレス入力を再アサートすることなく、1 つのア ドレスを最大 4 回まで読み出すことができます。シングル・リード・アクセスのセクションで説明したように、新しいアドレスを SRAM にロードするには、ADV/LD を LOW に駆動する必要があります。バースト・カウンタのシーケンスは MODE 入力信号によって決定される。MODEのLOW入力はリニアバーストモードを選択し、HIGHはインターリーブバーストシーケンスを選択する。どちらのバースト・カウンタもバースト・シーケンスでA0とA1を使用し、十分にインクリメントされるとラップアラウンドする。ADV/LDのHIGH入力は、チップイネーブル入力やWEの状態に関係なく内部バーストカウンタをインクリメントする。バースト・サイクルの最初にラッチされる。従って、アクセスの種類(読み出しまたは書き込み)はバースト・シーケンスを通して維持される。

シングル・ライト・アクセス

(1)CENがLOWにアサートされ、(2)CE1、CE2、CE3がすべてアクティブにアサートされ、 (3)WEがLOWにアサートされる。アドレス・バスに示されたアドレスがアドレス・レジスタにロードされる。ライト信号はコントロール・ロジック・ブロックにラッチされる。OE入力信号の状態に関係なく、データ・ラインは自動的に3ステートされる。こ れに よ り 、 外部 ロ ジ ッ ク はDQs とDQPX にデー タ を表示で き る よ う にな り ます。次のクロック立ち上がりで、DQsとDQPX(またはバイト・ライト動作のサブセット、詳細は9ページのリード/ライトの真理値表 を参照)入力に示されたデータがデバイスにラッチされ、書き込みが完了します。追加アクセス(読み出し/書き込み/選択解除)はこのサイクルで開始できる。書き込み動作中に書き込まれるデータは、BWX 信号によって制御される。CY7C1471V33 は、9 ページの読み出し/書き込みの真理値表で説明されているバイト書き込み機能を提供する。選択された BWX 入力を持つ入力 WE は、希望するバイトのみに選択的に書き込みます。バイト・ライト動作中に選択されなかったバイトは、変更されずに残ります。書き込み動作を単純化するために、同期自己タイミング書き込みメカニズムが提供されている。バイト書き込み機能が搭載されているため、読み出し/変更/書き込みシーケンスが大幅に簡素化され、単純なバイト書き込み操作に減らすことができます。CY7C1471V33は一般的なI/Oデバイスであるため、出力がアクティブの間はデバイスにデータを打ち込んではならない。DQs と DQPX 入力にデータを入力する前に、出力イネーブル(OE)を HIGH にディアサートすることができる。そうすることで、出力ドライバが3ステートされる。安全上の予防措置として、DQs と DQPX は、OE の状態に関係なく、書き込みサイクルのデータ部分で自動的にトライステートされる。

バースト書き込みアクセス

CY7C1471V33 にはバースト・カウンタが内蔵されており、アドレス入力を再アサートすることなく、1 つのア ドレスを供給して最大 4 回の書き込みを行うことができる。シングル・ライト・アクセスのセクションで説明したように、初期アドレスをロードするには ADV/LD を LOW に駆動する必要がある。その後のクロック立ち上がりでADV/LDがHIGHに駆動されると、チップ・イネーブル(CE1、CE2、CE3)、WE 入力は無視され、バースト・カウンタがインクリメントされる。正しいバイト・データを書き込むには、バースト・ライトの各サイクルで正しいBWX入力を駆動する必要がある。

スリープモード

ZZ 入力ピンは非同期入力である。ZZ をアサートすると、SRAM は省電力の「スリープ」モードになる。この「スリープ」モードに入るにも、スリープモードから抜けるにも 2 クロック・サイクルが必要である。このモードにある間、データの完全性は保証される。スリープ」モードに入るときに保留されているアクセスは有効とはみなされず、動作の完了も保証されない。スリープ・モードに入る前に、デバイスの選択を解除する必要がある。CE1、CE2、CE3は、ZZ入力がLOWに戻った後、tZZRECの間、非アクティブでなければならない。