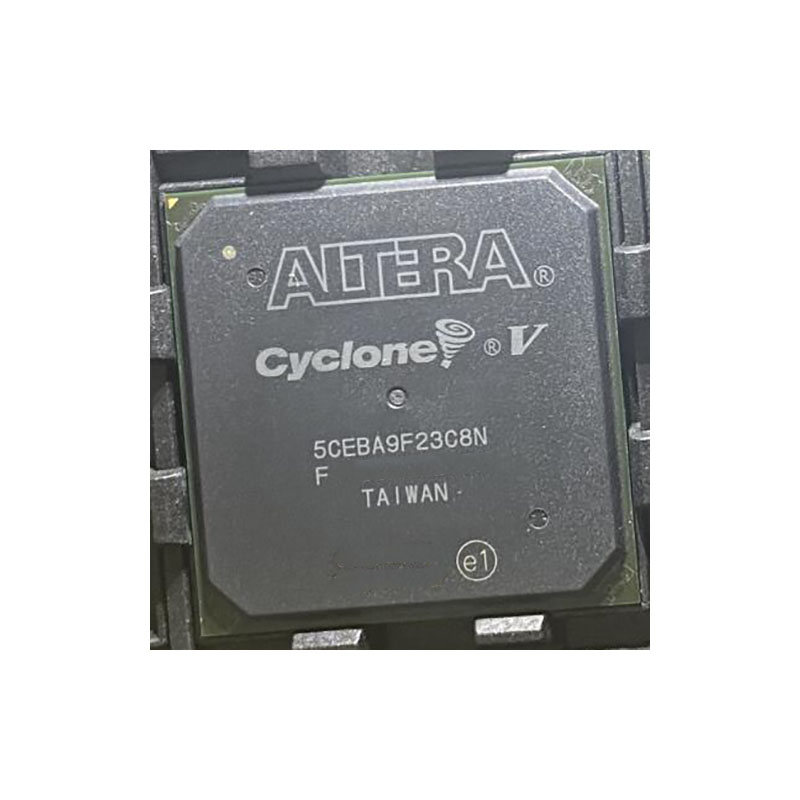

Описание:

Сайт CycloneV Устройства разработаны с учетом одновременного уменьшения энергопотребления, стоимости и время выхода на рынок требования; и растущие требования к пропускной способности для крупносерийных и чувствительных к стоимости приложений.

Cyclone V E оптимизированы для обеспечения минимальной стоимости системы и требуемой мощности для широкого спектра приложений общей логики и ЦОС.

Основные преимущества устройств Cyclone® V

Низкое энергопотребление

Создан на базе 28 нм техпроцесса TSMC с низким энергопотреблением (28LP) и включает в себя большое количество сложных блоков интеллектуальной собственности (IP)На 40% меньше энергопотребление по сравнению с устройством предыдущего поколения

Улучшенные возможности логической интеграции и дифференциации

8-входной адаптивный логический модуль (ALM)

До 13,59 мегабит (Мб) встроенной памяти

Блоки цифровой обработки сигналов (ЦОС) с переменной точностью

Увеличенная пропускная способность

- гигабит в секунду (Гбит/с) и 144 Гбит/с приемопередатчиков

- Контроллеры жесткой памяти

Система жесткого процессора (HPS) со встроенным Arm* Cortex* -A9 MPCore* процессор

Тесная интеграция двухъядерного процессора Arm* Cortex* -A9 MPCore*, жесткого IP и FPGA в одной системе-на-кристалле (SoC) Cyclone® V

Поддержка пиковой пропускной способности более 128 Гбит/с с интегрированной когерентностью данных между процессором и тканью FPGA.

Самая низкая стоимость системы

Для работы требуется только два напряжения на сердечнике

Поставляется в недорогой упаковке из проволочной ленты

Включает такие инновационные функции, как конфигурация по протоколу (CvP) и частичная реконфигурация

Характеристики

Технология

- 28-нм техпроцесс TSMC с низким энергопотреблением (28LP)

- 1,1 В напряжение на сердечнике

Упаковка

- Проволочная связка с низкогалогенными пакетами

- Несколько плотностей устройств с совместимыми размерами корпусов для беспрепятственной миграции между различными плотностями устройств

- Соответствует RoHS и имеет свинцовое покрытие(1)опции

Высокопроизводительная ткань FPGA Улучшенный 8-входовой ALM с четырьмя регистрами

Внутренние блоки памяти

- M10K-10-килобитные блоки памяти с мягким кодом коррекции ошибок (ECC)

- Блок логического массива памяти (MLAB)-640-битная распределенная LUTRAM, где в качестве памяти MLAB можно использовать до 25% ALM.

Встраиваемые жесткие IP-блоки

ЦОС с переменной точностью

- Встроенная поддержка до трех уровней точности обработки сигнала (три 9 x 9, два 18 x 18 или один 27 x 27 умножитель) в одном блоке DSP с переменной точностью

- 64-битный аккумулятор и каскад

- Встроенная внутренняя память коэффициентов

- Дозатор/субтрактор для повышения эффективности

Контроллер памяти DDR3, DDR2 и LPDDR2 с поддержкой 16 и 32 бит ECC

Встроенный трансивер ввода/вывода PCI Express* (PCIe*) Gen2 и Gen1 (x1, x2 или x4) с многофункциональной поддержкой, конечной точкой и корневым портом

Часовые сети

- Глобальная сеть синхронизации до 550 МГц

- Глобальные, квадрантные и периферийные тактовые сети

- Неиспользуемые сети часов можно отключить, чтобы снизить динамическую мощность.

Циклы с фазовой автоподстройкой (PLL)

- Прецизионный синтез тактовых импульсов, компенсация тактовой задержки и буферизация с нулевой задержкой (ZDB)

- Целочисленный и дробный режимы

ПЛИС Входы/выходы общего назначения (GPIO)

- LVDS-приемник 875 мегабит в секунду (Мбит/с) и LVDS-передатчик 840 Мбит/с

- Интерфейс внешней памяти 400 МГц/800 Мбит/с

- Оконечное устройство на кристалле (OCT)

- Поддержка 3,3 В с силой тока до 16 мА

Высокоскоростной последовательный интерфейс с низким энергопотреблением

- Скорость встроенного приемопередатчика от 614 Мбит/с до 6,144 Гбит/с

- Предварительный фазис передачи и эквализация приемника

- Динамическая частичная реконфигурация отдельных каналов

HPS (только для устройств Cyclone V SE, SX и ST)

- Одно- или двухъядерный процессор Arm Cortex-A9 MPCore - максимальная частота до 925 МГц с поддержкой симметричной и асимметричной многопроцессорной обработки

- Интерфейсные периферийные устройства-10/100/1000 Ethernet media access control (EMAC), контроллер USB 2.0 On-The-GO (OTG), контроллер четырех последовательных периферийных интерфейсов (QSPI), контроллер флэш-памяти NAND, контроллер Secure Digital/MultiMediaCard (SD/MMC), UART, сеть контроллеров (CAN), последовательный периферийный интерфейс (SPI), интерфейс I2C и до 85 HPS GPIO

интерфейсы

- Системные периферийные устройства - таймеры общего назначения, сторожевые таймеры, контроллер прямого доступа к памяти (DMA), менеджер конфигурации ПЛИС, а также менеджеры тактового генератора и сброса.

- Оперативная память и загрузочное ПЗУ на кристалле

- Мосты HPS-FPGA - включают мосты FPGA-to-HPS, HPS-to-FPGA и облегченный мост HPS-to-FPGA, которые позволяют ткани FPGA выдавать транзакции ведомым устройствам HPS и наоборот.

- Подсистема FPGA-to-HPS SDRAM controller - обеспечивает конфигурируемый интерфейс к многопортовому переднему концу (MPFE) контроллера HPS SDRAM

- Порт отладки Arm CoreSight™ JTAG, порт трассировки и хранилище трассировки на кристалле

Конфигурация

- Защита от несанкционированного доступа - комплексная защита конструкции для защиты ваших ценных инвестиций в ИС

- Улучшенные функции защиты по стандарту расширенного шифрования (AES)

- CvP

- Динамическая реконфигурация ПЛИС

- Активные последовательные (AS) x1 и x4, пассивные последовательные (PS), JTAG и быстрые пассивные параллельные (FPP) x8 и x16 варианты конфигурации

- Внутренняя очистка

- Частичная реконфигурация

Приложения:

Благодаря встроенным приемопередатчикам и контроллерам жесткой памяти Cyclone® V Устройства подходят для применения в промышленности, беспроводных и проводных сетях, в военной и автомобильной промышленности.